# (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.) **G09G 3/3233** (2016.01)

(52) CPC특허분류

**G09G 3/3233** (2013.01) G09G 2300/0452 (2013.01)

(21) 출원번호 10-2018-0097404

(22) 출원일자 **2018년08월21일**

심사청구일자 **없음**

(30) 우선권주장

1020180063604 2018년06월01일 대한민국(KR)

(11) 공개번호 10-2019-0137658

(43) 공개일자 2019년12월11일

(71) 출원인

삼성전자주식회사

경기도 수원시 영통구 삼성로 129 (매탄동)

(72) 발명자

김진호

경기도 용인시 기흥구 서그내로 31, 104동 1301 호(서천동, 용인서천 효성해링턴플레이스)

강기선

경기도 수원시 영통구 도청로 65, 5413동 1302호 (이의동, 자연앤 힐스테이트)

(뒷면에 계속)

(74) 대리인

정홍식, 김태헌

전체 청구항 수 : 총 12 항

(54) 발명의 명칭 디스플레이 패널

#### (57) 요 약

디스플레이 패널이 개시된다. 본 디스플레이 패널은, 글래스(Glass) 상에 형성되며 제 1 및 제 2 구동 회로를 포함하는 구동 회로층, 및 구동 회로층 위에 제 1 구동 회로와 전기적으로 연결되도록 실장되며 디스플레이 패널의 서브 픽셀을 구성하는 발광 소자를 포함하며, 제 1 구동 회로는, 상기 무기 발광 소자로 제공되는 구동 전류의 진폭을 제어하기 위한 PAM 구동 회로 및 상기 무기 발광 소자의 발광 시간(duration)을 제어하기 위한 PWM 구동 회로를 포함하고, 제 2 구동 회로는, 상기 구동 회로층에서 상기 제 1 구동 회로가 배치된 영역을 제외한 나머지 영역에 배치되며, 제 1 구동 회로를 구동하기 위한 제어 신호를 생성하여 제 1 구동 회로에 제공한다.

#### 대 표 도 - 도3

# 1000

(52) CPC특허분류

G09G 2320/0233 (2013.01) G09G 2320/0242 (2013.01) G09G 2330/028 (2013.01)

(72) 발명자

#### 신상민

경기도 수원시 영통구 청명로 132, 327동 704호(영 통동, 벽산삼익아파트)

### 이호섭

서울특별시 송파구 위례광장로 230, 201동 2104호 (장지동, 위례2차아이파크)

### 정영기

경기도 용인시 수지구 동천로63번길 10, 209동 1402호(동천동, 동천마을현대2차홈타운)

#### 명세서

#### 청구범위

#### 청구항 1

디스플레이 패널에 있어서,

글래스(Glass) 상에 형성되며, 제 1 및 제 2 구동 회로를 포함하는 구동 회로층; 및

상기 구동 회로층 위에 상기 제 1 구동 회로와 전기적으로 연결되도록 실장되며, 상기 디스플레이 패널의 서브 픽셀을 구성하는 무기 발광 소자;를 포함하며,

상기 제 1 구동 회로는,

상기 무기 발광 소자로 제공되는 구동 전류의 진폭을 제어하기 위한 PAM(Pulse Amplitude Modulation) 구동 회로 및 상기 무기 발광 소자의 발광 시간(duration)을 제어하기 위한 PWM(Pulse Width Modulation) 구동 회로를 포함하고,

상기 제 2 구동 회로는,

상기 구동 회로층에서 상기 제 1 구동 회로가 배치된 영역을 제외한 나머지 영역에 배치되며, 상기 제 1 구동 회로를 구동하기 위한 제어 신호를 생성하여 상기 제 1 구동 회로에 제공하는 디스플레이 패널.

#### 청구항 2

제 1 항에 있어서,

상기 디스플레이 패널은, 매트릭스 형태로 배치된 복수의 픽셀을 포함하고,

상기 복수의 픽셀 각각은, 적색(R) 무기 발광 소자를 포함하는 R 서브 픽셀, 녹색(G) 무기 발광 소자를 포함하는 G 서브 픽셀 및 청색(B) 무기 발광 소자를 포함하는 B 서브 픽셀을 포함하고,

상기 제 1 구동 회로는,

상기 구동 회로층에 상기 R, G, B 서브 픽셀 별로 형성되는 것을 특징으로 하는 디스플레이 패널.

#### 청구항 3

제 2 항에 있어서,

상기 디스플레이 패널의 각 서브 픽셀을 구성하는 복수의 제 1 구동 회로들 간의 편차로 인해 발생하는 상기 구동 전류의 진폭 편차는, 상기 구동 전류의 진폭을 설정하기 위해 상기 제 1 구동 회로로 인가되는 데이터 전압을 보정하여 보상되고,

상기 복수의 제 1 구동 회로들 간의 편차로 인해 발생하는 상기 구동 전류의 펄스 폭 편차는, 상기 구동 회로에 포함된 트랜지스터의 연결 구조를 통해 보상되는 것을 특징으로 하는 디스플레이 패널.

#### 청구항 4

제 2 항에 있어서,

상기 제 1 구동 회로는,

데이터 라인과 전류원 사이에 연결되어, 상기 전류원을 흐르는 전류를 상기 데이터 라인을 통해 외부로 제공하기 위한 제 1 트랜지스터;를 더 포함하고,

상기 PAM 구동 회로는,

상기 데이터 라인과 연결된 제 2 트랜지스터를 포함하고, 상기 제 2 트랜지스터를 통해 입력되며 상기 외부로 제공된 전류에 기초하여 보정된 진폭 설정 전압에 따라 상기 무기 발광 소자를 PAM 제어하고,

상기 PWM 구동 회로는,

상기 데이터 라인과 연결된 제 3 트랜지스터를 포함하고, 상기 제 3 트랜지스터를 통해 입력되는 필스 폭 설정 전압에 기초하여 상기 무기 발광 소자를 PWM 제어하는 것을 특징으로 하는 디스플레이 패널.

#### 청구항 5

제 4 항에 있어서,

상기 제 2 구동 회로는,

상기 매트릭스의 복수의 라인 중 하나의 라인의 복수의 픽셀을 구성하는 무기 발광 소자들을 구동하기 위한 복수의 제 1 구동 회로에 포함된 상기 제 1 트랜지스터를 온 시키기 위한 제 1 제어 신호를 영상 프레임 별로 생성하고, 상기 생성된 제 1 제어 신호를 상기 하나의 라인의 상기 제 1 트랜지스터로 제공하기 위한 제 1 구동부;를 포함하는 것을 특징으로 하는 디스플레이 패널.

#### 청구항 6

제 5 항에 있어서,

상기 제 1 구동부는,

하나의 영상 프레임에 대해, 하나의 라인의 상기 제 1 트랜지스터를 온 시키기 위한 제 1 제어 신호를 생성하고, 다음 영상 프레임에 대해, 상기 하나의 라인 다음의 라인의 상기 제 1 트랜지스터를 온 시키기 위한 제 1 제어 신호를 생성하는 것을 특징으로 하는 디스플레이 패널.

#### 청구항 7

제 5 항에 있어서,

상기 제 1 구동부는,

하나의 라인에 대한 상기 제 1 제어 신호를 생성하기 위한 제 1 회로를 상기 복수의 라인의 개수만큼 포함하고,

하나의 라인에 대한 제 1 회로의 출력 신호는, 상기 하나의 라인의 다음 라인에 대한 제 1 회로의 스타트 신호로 입력되는 것을 특징으로 하는 디스플레이 패널.

#### 청구항 8

제 4 항에 있어서,

상기 제 2 구동 회로는,

상기 매트릭스의 각 라인의 복수의 픽셀을 구성하는 무기 발광 소자들을 구동하기 위한 복수의 구동 회로에 포함된 상기 제 2 및 제 3 트랜지스터를, 하나의 영상 프레임에 대해 라인 별로 온 시키기 위한 제 2 및 제 3 제 어 신호를 생성하고, 상기 생성된 제 2 및 제 3 제어 신호를 상기 각 라인의 상기 제 2 및 제 3 트랜지스터로 제공하기 위한 제 2 구동부;를 포함하는 것을 특징으로 하는 디스플레이 패널.

#### 청구항 9

제 8 항에 있어서,

상기 제 2 구동부는,

상기 제 3 트랜지스터를 라인 별로 순차적으로 온 시키기 위한 상기 제 3 제어 신호를 생성하여 상기 각 라인의 제 3 트랜지스터에 제공한 뒤, 상기 제 2 트랜지스터를 라인 별로 순차적으로 온 시키기 위한 상기 제 2 제어 신호를 생성하여 상기 각 라인의 제 2 트랜지스터로 제공하는 것을 특징으로 하는 디스플레이 패널.

#### 청구항 10

제 8 항에 있어서,

상기 제 2 구동부는,

하나의 라인에 대한 상기 제 2 제어 신호 또는 제 3 제어 신호를 생성하기 위한 제 2 회로를 상기 복수의 라인의 개수의 2배만큼 포함하고,

하나의 라인에 대한 제 2 회로는, 상기 하나의 라인의 이전 라인에 대한 제 2 회로의 출력 신호를 스타트 신호로 입력받고,

상기 하나의 라인에 대한 제 2 회로의 출력 신호는, 상기 이전 라인에 대한 제 2 회로의 리셋 신호로 입력되는 것을 특징으로 하는 디스플레이 패널.

#### 청구항 11

제 2 항에 있어서,

상기 구동 회로층은,

상기 R, G, B 서브 픽셀 중 하나를 선택하기 위한 먹스(Mux)회로, 상기 디스플레이 패널에서 발생하는 정전기를 방전시키기 위한 ESD(Electro Static Discharge) 회로, 상기 제 1 및 제 2 구동 회로를 구동하는 전원 공급을 위한 전원 회로, 상기 제 1 및 제 2 구동 회로를 구동하는 클럭을 제공하기 위한 클럭 제공 회로 중 적어도 하나를 더 포함하는 것을 특징으로 하는 디스플레이 패널.

#### 청구항 12

제 1 항에 있어서,

상기 무기 발광 소자는,

100 마이크로미터 이하의 크기를 갖는 마이크로 LED인 것을 특징으로 하는 디스플레이 패널.

#### 발명의 설명

#### 기술분야

[0001] 본 개시는 디스플레이 패널에 관한 것으로, 보다 상세하게는, 발광 소자가 픽셀을 구성하는 디스플레이 패널에 관한 것이다.

### 배경기술

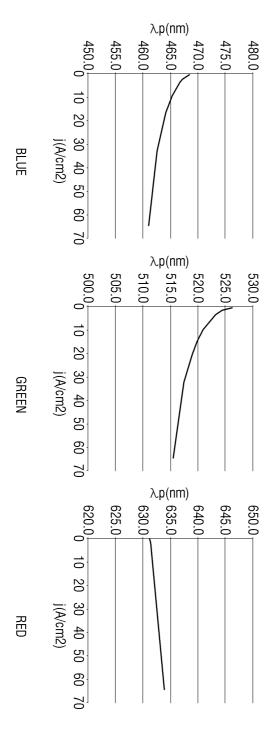

- [0002] 종래, 적색 LED, 녹색 LED, 청색 LED와 같은 무기 발광 소자(이하 LED라 칭함)를 서브 픽셀로 구동하는 디스플 레이 패널에서는, 구동 전류의 진폭을 이용하여 서브 픽셀의 계조를 표현하였다.

- [0003] 이 경우, 구동 전류의 진폭에 따라, 발광하는 빛의 계조뿐만 아니라 파장도 함께 변하게 되어 영상의 색 재현성이 감소된다. 도 1은 청색 LED, 녹색 LED 및 적색 LED를 흐르는 구동 전류의 크기(또는 진폭)에 따른 파장 변화를 도시하고 있다.

# 발명의 내용

#### 해결하려는 과제

- [0004] 본 개시의 목적은 글래스(Glass) 기판 상에 실장되는 무기 발광 소자인 LED가 안정적으로 동작되도록 하는 구동 회로를 포함하여 이루어진 디스플레이 패널을 제공함에 있다.

- [0005] 본 개시의 다른 목적은, 글래스 기판 상에 실장되는 무기 발광 소자인 LED를 구동하는 구동 회로의 설계를 최적화하여, 고밀도 집적에 적합한 구동 회로를 포함하는 디스플레이 패널을 제공함에 있다.

- [0006] 본 개시의 또 다른 목적은, 입력되는 영상 신호에 대해, 글래스 기판 상에 실장되는 무기 발광 소자인 LED를 통해, 향상된 색재현성을 제공하는 디스플레이 패널 및 이를 채용한 디스플레이 장치를 제공함에 있다.

#### 과제의 해결 수단

[0007] 이상과 같은 목적을 달성하기 위한 본 개시의 일 실시 예에 따른 디스플레이 패널은, 글래스(Glass) 상에 형성되며, 제 1 및 제 2 구동 회로를 포함하는 구동 회로층 및 상기 구동 회로층 위에 상기 제 1 구동 회로와 전기

적으로 연결되도록 실장되며, 상기 디스플레이 패널의 서브 픽셀을 구성하는 무기 발광 소자를 포함하며, 상기 제 1 구동 회로는, 상기 무기 발광 소자로 제공되는 구동 전류의 진폭을 제어하기 위한 PAM(Pulse Amplitude Modulation) 구동 회로 및 상기 무기 발광 소자의 발광 시간(duration)을 제어하기 위한 PWM(Pulse Width Modulation) 구동 회로를 포함하고, 상기 제 2 구동 회로는, 상기 구동 회로층에서 상기 제 1 구동회로가 배치된 영역을 제외한 나머지 영역에 배치되며, 상기 제 1 구동 회로를 구동하기 위한 제어 신호를 생성하여 상기제 1 구동 회로에 제공한다.

- [0008] 또한, 상기 디스플레이 패널은, 매트릭스 형태로 배치된 복수의 픽셀을 포함하고, 상기 복수의 픽셀 각각은, 적색(R) 무기 발광 소자를 포함하는 R 서브 픽셀, 녹색(G) 무기 발광 소자를 포함하는 G 서브 픽셀 및 청색(B) 무기 발광 소자를 포함하는 B 서브 픽셀을 포함하고, 상기 제 1 구동 회로는, 상기 구동 회로층에 상기 R, G, B 서브 픽셀 별로 형성될 수 있다.

- [0009] 또한, 상기 디스플레이 패널의 각 서브 픽셀을 구성하는 복수의 제 1 구동 회로들 간의 편차로 인해 발생하는 상기 구동 전류의 진폭 편차는, 상기 구동 전류의 진폭을 설정하기 위해 상기 제 1 구동 회로로 인가되는 데이터 전압 을 보정하여 보상되고, 상기 복수의 제 1 구동 회로들 간의 편차로 인해 발생하는 상기 구동 전류의 필스 폭 편차는, 상기 구동 회로에 포함된 트랜지스터의 연결 구조를 통해 보상될 수 있다.

- [0010] 또한, 상기 제 1 구동 회로는, 데이터 라인과 전류원 사이에 연결되어, 상기 전류원을 흐르는 전류를 상기 데이터 라인을 통해 외부로 제공하기 위한 제 1 트랜지스터를 더 포함하고, 상기 PAM 구동 회로는, 상기 데이터 라인과 연결된 제 2 트랜지스터를 포함하고, 상기 제 2 트랜지스터를 통해 입력되며 상기 외부로 제공된 전류에 기초하여 보정된 진폭 설정 전압에 따라 상기 무기 발광 소자를 PAM 제어하고, 상기 PWM 구동 회로는, 상기 데이터 라인과 연결된 제 3 트랜지스터를 포함하고, 상기 제 3 트랜지스터를 통해 입력되는 펄스 폭 설정 전압에 기초하여 상기 무기 발광 소자를 PWM 제어할 수 있다.

- [0011] 또한, 상기 제 2 구동 회로는, 상기 매트릭스의 복수의 라인 중 하나의 라인의 복수의 픽셀을 구성하는 무기 발광 소자들을 구동하기 위한 복수의 제 1 구동 회로에 포함된 상기 제 1 트랜지스터를 온 시키기 위한 제 1 제어 신호를 영상 프레임 별로 생성하고, 상기 생성된 제 1 제어 신호를 상기 하나의 라인의 상기 제 1 트랜지스터로 제공하기 위한 제 1 구동부를 포함할 수 있다.

- [0012] 또한, 상기 제 1 구동부는, 하나의 영상 프레임에 대해, 하나의 라인의 상기 제 1 트랜지스터를 온 시키기 위한 제 1 제어 신호를 생성하고, 다음 영상 프레임에 대해, 상기 하나의 라인 다음의 라인의 상기 제 1 트랜지스터를 온 시키기 위한 제 1 제어 신호를 생성할 수 있다.

- [0013] 또한, 상기 제 1 구동부는, 하나의 라인에 대한 상기 제 1 제어 신호를 생성하기 위한 제 1 회로를 상기 복수의 라인의 개수만큼 포함하고, 하나의 라인에 대한 제 1 회로의 출력 신호는, 상기 하나의 라인의 다음 라인에 대한 제 1 회로의 스타트 신호로 입력될 수 있다.

- [0014] 또한, 상기 제 2 구동 회로는, 상기 매트릭스의 각 라인의 복수의 픽셀을 구성하는 무기 발광 소자들을 구동하기 위한 복수의 구동 회로에 포함된 상기 제 2 및 제 3 트랜지스터를, 하나의 영상 프레임에 대해 라인 별로 온시키기 위한 제 2 및 제 3 제어 신호를 생성하고, 상기 생성된 제 2 및 제 3 제어 신호를 상기 각 라인의 상기제 2 및 제 3 트랜지스터로 제공하기 위한 제 2 구동부를 포함할 수 있다.

- [0015] 또한, 상기 제 2 구동부는, 상기 제 3 트랜지스터를 라인 별로 순차적으로 온 시키기 위한 상기 제 3 제어 신호를 생성하여 상기 각 라인의 제 3 트랜지스터에 제공한 뒤, 상기 제 2 트랜지스터를 라인 별로 순차적으로 온 시키기 위한 상기 제 2 제어 신호를 생성하여 상기 각 라인의 제 2 트랜지스터로 제공할 수 있다.

- [0016] 또한, 상기 제 2 구동부는, 하나의 라인에 대한 상기 제 2 제어 신호 또는 제 3 제어 신호를 생성하기 위한 제 2 회로를 상기 복수의 라인의 개수의 2배만큼 포함하고, 하나의 라인에 대한 제 2 회로는, 상기 하나의 라인의 이전 라인에 대한 제 2 회로의 출력 신호를 스타트 신호로 입력받고, 상기 하나의 라인에 대한 제 2 회로의 출력 신호는, 상기 이전 라인에 대한 제 2 회로의 리셋 신호로 입력될 수 있다.

- [0017] 또한, 상기 구동 회로층은, 상기 R, G, B 서브 픽셀 중 하나를 선택하기 위한 먹스(Mux)회로, 상기 디스플레이 패널에서 발생하는 정전기를 방전시키기 위한 ESD(Electro Static Discharge) 회로, 상기 제 1 및 제 2 구동 회로를 구동하는 전원 공급을 위한 전원 회로, 상기 제 1 및 제 2 구동 회로를 구동하는 클럭을 제공하기 위한 클럭 제공 회로 중 적어도 하나를 더 포함할 수 있다.

- [0018] 또한, 상기 무기 발광 소자는, 100 마이크로미터 이하의 크기를 갖는 마이크로 LED일 수 있다.

#### 발명의 효과

[0019] 이상 설명한 바와 같이 본 개시의 다양한 실시 예에 따르면, 디스플레이 패널에 포함된 무기 발광 소자의 계조에 따른 파장 변화를 방지할 수 있다. 또한, 디스플레이 패널을 구성하는 무기 발광 소자의 얼룩이나 색상을 보정할 수 있다. 또한, 모듈 형태의 디스플레이 패널을 조합하여 대면적의 타일드(tiled) 디스플레이 패널을 구성할 경우에도 각 디스플레이 패널 모듈 간의 휘도나 색상 차이를 보정할 수 있다.

#### 도면의 간단한 설명

- [0020] 도 1은 청색 LED, 녹색 LED 및 적색 LED를 흐르는 구동 전류의 크기에 따른 파장 변화를 나타내는 그래프,

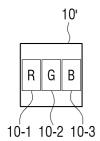

- 도 2a는 본 개시의 일 실시 예에 따른 디스플레이 패널의 픽셀 구조를 설명하기 위한 도면,

- 도 2b는 본 개시의 다른 일 실시 예에 따른 서브 픽셀 구조를 도시한 도면,

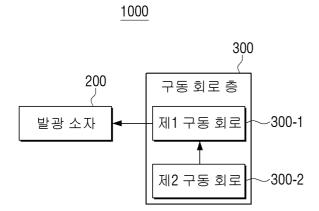

- 도 3은 본 개시의 일 실시 예에 따른 디스플레이 패널의 블럭도,

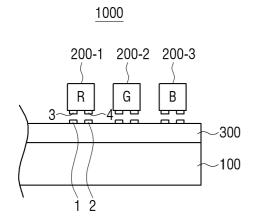

- 도 4a는 본 개시의 일 실시 예에 따른 디스플레이 패널의 단면도,

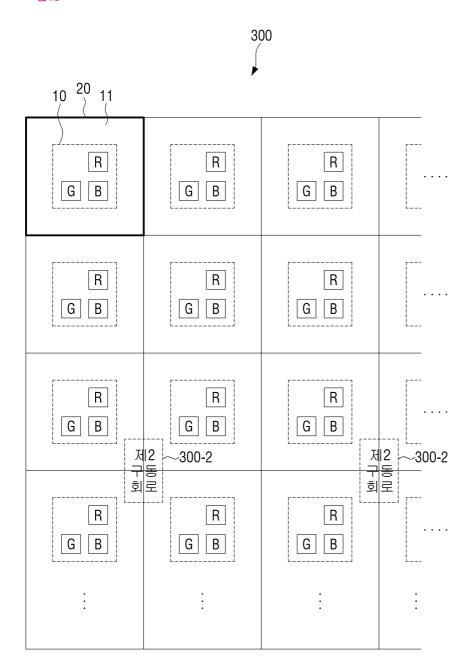

- 도 4b는 본 개시의 일 실시 예에 따른 구동 회로층의 평면도,

- 도 5a는 본 개시의 다른 일 실시 예에 따른 디스플레이 패널의 단면도,

- 도 5b는 본 개시의 다른 일 실시 예에 따른 구동 회로층의 평면도,

- 도 6은 본 개시의 일 실시 예에 따른 디스플레이 패널에 포함된 하나의 서브 픽셀과 관련된 구성을 도시한 구성 도,

- 도 7은 본 개시의 일 실시 예에 따른 제 1 구동 회로의 상세 회로도,

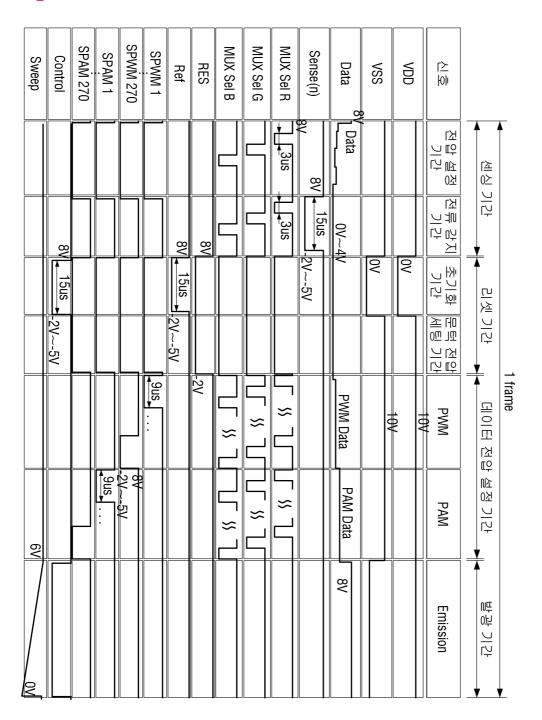

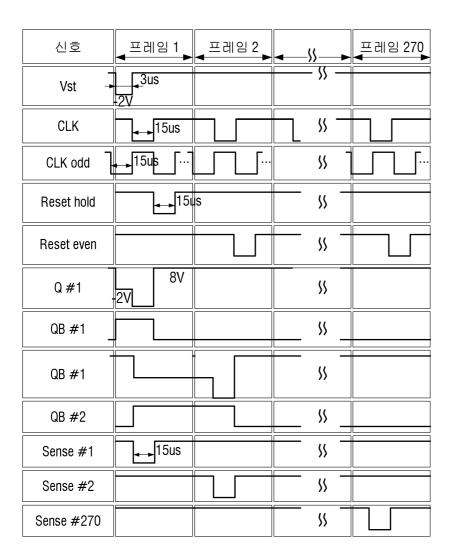

- 도 8은 디스플레이 패널에 포함된 제 1 구동 회로를 구동하기 위한 각종 신호의 타이밍도,

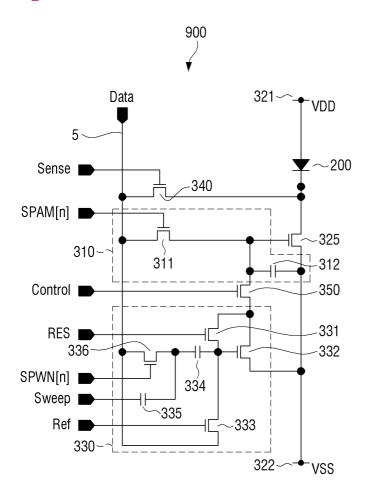

- 도 9는 제 1 구동 회로에 포함된 트랜지스터들이 모두 NMOSFET으로 구현된 제 1 구동 회로의 회로도,

- 도 10a 내지 도 10c는 제 1 구동 회로의 구성 및 동작을 설명하기 위한 도면,

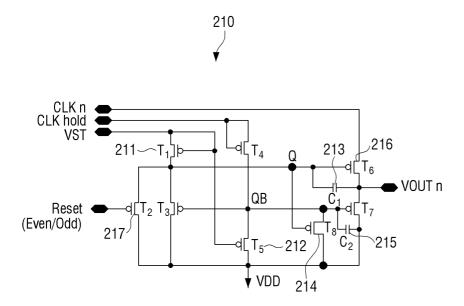

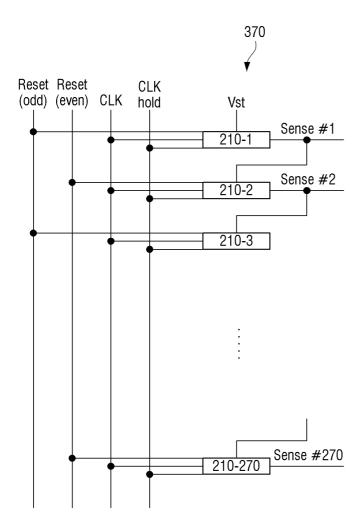

- 도 11a 내지 도 11c는 제 2 구동 회로의 구성 및 동작을 설명하기 위한 도면, 및

- 도 12는 본 개시의 일 실시 예에 따른 디스플레이 장치의 구성도이다.

#### 발명을 실시하기 위한 구체적인 내용

- [0021] 본 개시를 설명함에 있어, 관련된 공지 기술에 대한 구체적인 설명이 본 개시의 요지를 불필요하게 흐릴 수 있다고 판단되는 경우 그 상세한 설명을 생략한다. 또한, 동일한 구성의 중복 설명은 되도록 생략하기로 한다.

- [0022] 이하의 설명에서 사용되는 구성요소에 대한 접미사 "부"는 명세서 작성의 용이함만이 고려되어 부여되거나 혼용되는 것으로서, 그 자체로 서로 구별되는 의미 또는 역할을 갖는 것은 아니다.

- [0023] 본 개시에서 사용한 용어는 실시 예를 설명하기 위해 사용된 것으로, 본 개시를 제한 및/또는 한정하려는 의도 가 아니다. 단수의 표현은 문맥상 명백하게 다르게 뜻하지 않는 한, 복수의 표현을 포함한다.

- [0024] 본 개시에서, '포함하다' 또는 '가지다' 등의 용어는 명세서상에 기재된 특징, 숫자, 단계, 동작, 구성요소, 부품 또는 이들을 조합한 것이 존재함을 지정하려는 것이지, 하나 또는 그 이상의 다른 특징들이나 숫자, 단계, 동작, 구성요소, 부품 또는 이들을 조합한 것들의 존재 또는 부가 가능성을 미리 배제하지 않는 것으로 이해되어야 한다.

- [0025] 본 개시에서 사용된 "제1," "제2," "첫째," 또는 "둘째," 등의 표현들은 다양한 구성요소들을, 순서 및/또는 중요도에 상관없이 수식할 수 있고, 한 구성요소를 다른 구성요소와 구분하기 위해 사용될 뿐 해당 구성요소들을 한정하지 않는다.

- [0026] 어떤 구성요소(예: 제1 구성요소)가 다른 구성요소(예: 제2 구성요소)에 "(기능적으로 또는 통신적으로) 연결되어((operatively or communicatively) coupled with/to)" 있다거나 "접속되어(connected to)" 있다고 언급된 때에는, 상기 어떤 구성요소가 상기 다른 구성요소에 직접적으로 연결되거나, 다른 구성요소(예: 제3 구성요

소)를 통하여 연결될 수 있다고 이해되어야 할 것이다. 반면에, 어떤 구성요소(예: 제1 구성요소)가 다른 구성요소(예: 제2 구성요소)에 "직접 연결되어" 있다거나 "직접 접속되어" 있다고 언급된 때에는, 상기 어떤 구성요소와 상기 다른 구성요소 사이에 다른 구성요소(예: 제 3 구성요소)가 존재하지 않는 것으로 이해될 수 있다.

- [0027] 본 개시의 실시 예들에서 사용되는 용어들은 다르게 정의되지 않는 한, 해당 기술 분야에서 통상의 지식을 가진 자에게 통상적으로 알려진 의미로 해석될 수 있다.

- [0028] 이하에서 첨부된 도면을 참조하여 본 개시의 다양한 실시 예를 상세히 설명한다.

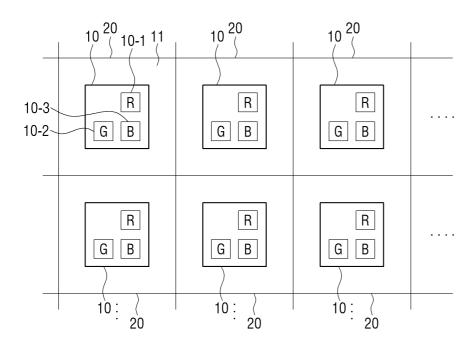

- [0029] 도 2a는 본 개시의 일 실시 예에 따른 디스플레이 패널(1000)의 픽셀 구조를 설명하기 위한 도면이다. 도 2a에 도시된 바와 같이, 디스플레이 패널(1000)은 매트릭스 형태로 배열된 복수의 픽셀(10)을 포함할 수 있다.

- [0030] 이때, 각 픽셀(10)은 복수의 서브 픽셀(10-1 내지 10-3)을 포함할 수 있다. 예를 들어, 디스플레이 패널(1000)에 포함된 하나의 픽셀(10)은 적색(R) 서브 픽셀(10-1), 녹색(G) 서브 픽셀(10-2)및 청색(B) 서브 픽셀(10-3)과 같은 3종류의 서브 픽셀을 포함할 수 있다. 즉, R, G, B 서브 픽셀 한 세트가 디스플레이 패널(1000)의 하나의 단위 픽셀을 구성할 수 있다.

- [0031] 한편, 도 2a를 참조하면, 디스플레이 패널(1000)에서 하나의 픽셀 영역(20)은, 픽셀(10)이 차지하는 영역과 주변의 나머지 영역(11)을 포함하는 것을 볼 수 있다.

- [0032] 구체적으로, 픽셀이 차지하는 영역(10)에는 도시된 바와 같이, R, G, B 서브 픽셀들(10-1 내지 10-3)이 포함될수 있는데, 이때, R 서브 픽셀(10-1)은 R 발광 소자 및 R 발광 소자를 구동하기 위한 제 1 구동 회로를, G 서브 픽셀(10-2)은 G 발광 소자 및 G 발광 소자를 구동하기 위한 제 1 구동 회로를, 그리고, B 서브 픽셀(10-3)은 B 발광 소자 및 B 발광 소자를 구동하기 위한 제 1 구동 회로를 각각 포함할 수 있다.

- [0033] 한편, 픽셀(10) 주변의 나머지 영역(11)에는, 제 1 구동 회로를 구동하기 위한 제 2 구동 회로를 포함하여 각종 회로들이 실시 예에 따라 포함될 수 있다. 이에 관한 자세한 내용은 후술하기로 한다.

- [0034] 도 2b는 본 개시의 다른 일 실시 예에 따른 서브 픽셀 구조를 도시한 도면이다. 도 2a를 참조하면, 하나의 픽셀 (10) 내에서 서브 픽셀들(10-1 내지 10-3)은 좌우가 뒤바뀐 L자 모양으로 배열된 것을 볼 수 있다. 그러나, 실시 예가 이에 한정되는 것은 아니며, 도 2B에 도시된 바와 같이, R, G, B 서브 픽셀(10-1 내지 10-3)이 픽셀 (10') 내부에서 일렬로 배치될 수도 있다. 다만, 이러한 서브 픽셀의 배치 형태는 일 예일 뿐이고, 복수의 서브 픽셀은 각 픽셀 내에서 다양한 형태로 배치될 수 있음은 물론이다.

- [0035] 한편, 상술한 예에서는 픽셀이 3종류의 서브 픽셀로 구성되는 것으로 설명하였으나, 이에 한정되는 것이 아님은 물론이다. 가령, 픽셀은 R, G, B, W(white)와 같이 4종류의 서브 픽셀로 구현될 수도 있고, 실시 예에 따라 얼마든지 다른 개수의 서브 픽셀이 하나의 픽셀을 구성할 수도 있음은 물론이다. 이하에서는, 설명의 편의를위해, 픽셀(10)이 R, G, B와 같은 세 종류의 서브 픽셀로 구성된 경우를 예로 들어 설명하기로 한다.

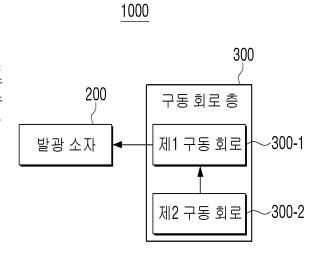

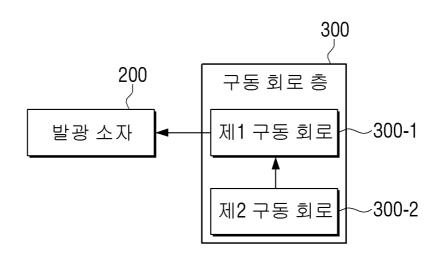

- [0036] 도 3은 본 개시의 일 실시 예에 따른 디스플레이 패널의 블럭도이다. 도 3에 따르면, 디스플레이 패널(1000)은 구동 회로층(300) 및 발광 소자(200)를 포함한다. 이때, 후술할 바와 같이, 디스플레이 패널(1000)은 글래스 (100) 상에 제 1 구동 회로(300-1) 및 제 2 구동 회로(300-2)를 포함하는 구동 회로층(300)이 형성되고, 구동 회로층(300) 위에 발광 소자(200)가 배치되는 구조를 가질 수 있다.

- [0037] 발광 소자(200)는 디스플레이 패널(1000)의 서브 픽셀(10-1 내지 10-3)을 구성하며, 구동 회로(300)의 구동에 따라 빛을 발광한다. 발광 소자(200)는 발광하는 빛의 색상에 따라 복수의 종류가 있을 수 있다. 예를 들어, 적색 색상의 빛을 발광하는 적색(R) 발광 소자, 녹색 색상의 빛을 발광하는 녹색(G) 발광 소자 및 청색 색상의 빛을 발광하는 청색(B) 발광 소자가 있을 수 있다.

- [0038] 한편, 도 2a에서 전술한 바와 같이, 서브 픽셀의 종류는 서브 픽셀을 구성하는 발광 소자(200)의 종류에 따라 결정될 수 있다. 즉, R 발광 소자는 R 서브 픽셀(10-1)을, G 발광 소자는 G 서브 픽셀(10-2)을, 그리고, B 발광 소자는 B 서브 픽셀(10-3)을 구성할 수 있다. 여기서, 발광 소자(200)는, 유기 재료를 이용하여 제작되는 OLED(Organic Light Emitting Diode)와는 다른, 무기 재료를 이용하여 제작되는 무기 발광 소자일 수 있다. 이하에서, LED는 OLED와 구별되는 무기 발광 소자를 의미한다.

- [0039] 한편, 본 개시의 일 실시 예에 따르면, 무기 발광 소자는, 마이크로 LED(Light Emitting Diode)(u-LED)일 수 있다. 마이크로 LED는 백라이트나 컬러 필터 없이 스스로 빛을 내는 100 마이크로미터(μm) 이하 크기의 초소형 무기 발광 소자를 말한다.

- [0040] 구동 회로층(300)은 발광 소자(200)를 구동하기 위한 각종 회로를 포함한다. 특히, 구동 회로층(300)에는 발광 소자(200)를 구동하기 위한 제 1 구동 회로(300-1) 및 제 1 구동 회로(300-1)를 구동하기 위한 제 2 구동 회로 (300-2)가 포함될 수 있다.

- [0041] 구체적으로, 제 1 구동 회로(300-1)는 발광 소자(200)를 구동하여 서브 픽셀 단위로 계조를 표현할 수 있다. 전술한 바와 같이 디스플레이 패널(1000)은 발광 소자 단위로 서브 픽셀이 구성되므로, 동일한 단일 색으로 발광하는 복 수의 LED를 백라이트로 사용하는 LCD(Liquid Crystal Display) 패널과 달리, 제 1 구동 회로(300-1)는 발광 소자(200)를 구동하여 서브 픽셀 단위로 계조를 표현할 수 있다.

- [0042] 이를 위해, 디스플레이 패널(1000)에 포함된 각 서브 픽셀은, 발광 소자(200) 및 발광 소자(200)를 구동하기 위한 제 1 구동 회로(300-1)로 구현될 수 있다. 즉, 각 발광 소자(200)를 구동하기 위한 제 1 구동 회로(300-1)가 구동 회로층(300)에 각 서브 픽셀별로 존재할 수 있다.

- [0043] 한편, 본 개시의 일 실시 예에 따르면, 제 1 구동 회로(300-1)는 발광 소자(200)를 PAM(Pulse Amplitude Modulation) 및 PWM(Pulse Width Modulation) 구동할 수 있다. 즉, 제 1 구동 회로(300-1)는 발광 소자(200)를 구동하는 구동 전류의 진폭과 펄스 폭을 함께 제어할 수 있고, 진폭과 펄스 폭이 함께 제어된 구동 전류를 발광소자(200)로 제공할 수 있다.

- [0044] 여기서, 구동 전류의 진폭과 펄스 폭이 "함께" 제어된다고 함은, 구동 전류의 진폭과 펄스 폭이 시간적으로 동시에 제어된다는 것을 의미하는 것은 아니며, 계조 표현을 위해 PAM 구동 방식과 PWM 구동 방식이 함께 이용된다는 것을 의미한다.

- [0045] 구체적으로, PWM 구동 방식은 발광 소자(200)의 발광 시간에 따라 계조를 표현하는 방식이다. 따라서, PWM 방식으로 발광 소자(200)를 구동하는 경우 구동 전류의 진폭이 동일하더라도 발광 시간을 달리하여 다양한 계조를 표현할 수 있게 된다. 이에 따라, PAM 방식만으로 LED를 구동하여 LED(특히, 마이크로 LED)가 발광하는 빛의 파장이 계조에 따라 변화하는 문제를 해결할 수 있게 된다.

- [0046] 이를 위해, 제 1 구동 회로(300-1)는 전류원, PAM 구동 회로 및 PWM 구동 회로를 각 서브 픽셀 별로 포함할 수 있는데, 이에 관한 보다 자세한 내용은 후술하기로 한다.

- [0047] 제 2 구동 회로(300-2)는 제 1 구동 회로(300-1)를 구동하기 위한 구동 회로이다. 즉, 제 2 구동 회로(300-2)는 제 1 구동 회로(300-1)의 동작을 위한 제어 신호를 생성하여 제 1 구동 회로(300-1)로 제공할 수 있다.

- [0048] 예를 들어, 제 2 구동 회로(300-2)는 제 1 구동 회로(300-1)에 포함된 PAM 구동 회로 및 PWM 구동 회로를 구동하기 위한 제어 신호를 각각 생성하여 PAM 구동 회로 및 PWM 구동 회로로 각각 제공할 수 있다. 또한, 제 2 구동 회로(300-2)는, 도 7을 참조할 때, 제 1 구동 회로(300-1)에 포함된 전류원(320)을 흐르는 전류를 데이터 라인(5)을 통해 외부로 제공하기 위한 제 1 트랜지스터(340)의 온/오프를 제어하기 위한 제어 신호를 생성하여 제 1 트랜지스터(340)로 제공할 수 있다.

- [0049] 이때, 제 2 구동 회로(300-2)는 매트릭스 형태로 배열된 디스플레이 패널의 픽셀들을 라인 단위로 구동할 수 있다. 즉, 제 2 구동 회로(300-2)는 매트릭스의 한 라인에 포함된 픽셀들을 구성하는 서브 픽셀들에 포함된 제 1 구동 회로들(300-1)을 구동하고, 다음 라인에 포함된 픽셀들을 구성하는 서브 픽셀들에 포함된 제 1 구동 회로들(300-1)을 구동하는 방식으로, 라인별로 디스플레이 패널(1000)에 포함된 제 1 구동 회로(300-1)들을 구동할수 있다.

- [0050] 이와 같이, 제 2 구동 회로(300-2)는 매트릭스의 가로 라인 단위(또는 행 단위)로 복수의 픽셀(또는 서브 픽셀)을 구동하게 되므로, 일명 "게이트 드라이버"로 불릴 수 있다. 그러나, 명칭으로 구성이 한정되는 것은 아니며, 가령, PWM 구동 회로 및 PAM 구동 회로를 구동하는 제어 신호를 생성하는 제 2 구동 회로(300-2) 부분을 PWM/PAM 드라이버로, 제 1 트랜지스터(340)의 온/오프를 제어하는 제어 신호를 생성하는 제 2 구동 회로(300-2) 부분을 센스(Sense) 드라이버로 각각 기능에 따라 나누어 부를 수도 있다.

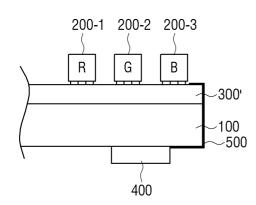

- [0051] 도 4a는 본 개시의 일 실시 예에 따른 디스플레이 패널(1000)의 단면도이다. 도 4a에서는 설명의 편의를 위해, 디스플레이 패널(1000)에 포함된 하나의 픽셀만을 도시하였다.

- [0052] 도 4a에 따르면, 구동 회로층(300)은 글래스(Glass)(100) 상에 형성되며, 발광 소자 R, G, B(200-1 내지 200-3) 각각은 구동 회로층(300) 위에 배치되어 디스플레이 패널(1000)의 서브 픽셀(10-1 내지 10-3)을 각각 구성한다.

- [0053] 이와 같이, 글래스(100) 상에 구동 회로층(300)과 발광 소자(200-1 내지 200-3)층이 형성되는 형태의 디스플레이 패널(1000)을 COG(Chip On Glass) 타입의 디스플레이 패널이라 칭할 수 있다. COG 타입의 디스플레이 패널은, 합성수지 등과 같은 기판상에 구동 회로와 발광 소자 층이 형성되는 COB(Chip On Board) 타입의 디스플레이 패널과는 구별된다. 구동 회로층(300)은 TFT(Thin Film Transistor)로 구현되어 TFT 층을 이룰 수 있다. 이때, 글래스(100) 상에 형성된 구동 회로층(300)과 글래스(100)를 더하여 TFT 패널 또는 글래스 기판이라 부를 수도 있다. 글래스 기판을 구성하는 글래스(100)의 종류나 특성은 본 개시의 요지와 무관하므로, 이하 자세한 설명은 생략한다.

- [0054] 한편, 도면에 명확히 구분하여 도시하지는 않았지만, 구동 회로층(300)에는 각 발광 소자(200-1 내지 200-3)를 구동하기 위한 제 1 구동 회로(300-1)가 발광 소자(200-1 내지 200-3)별로 존재한다. 따라서, 발광 소자 R, G, B(200-1 내지 200-3) 각각은 대응하는 제 1 구동 회로(300-1)와 전기적으로 연결되도록 구동 회로층(300) 위에 각각 실장 내지 배치되게 된다.

- [0055] 구체적으로, 도 4a에 도시된 바와 같이, R 발광 소자(200-1)는 R 발광 소자(200-1)의 애노드 전극(3) 및 캐소드 전극(4)이 R 발광 소자(200-1)를 구동하기 위한 제 1 구동 회로(300-1)상에 형성된 애노드 전극(1) 및 캐소드 전극(2)에 각각 연결되도록 실장 내지 배치될 수 있으며, 이는 G 발광 소자(200-2) 및 B 발광 소자(200-3)도 마찬가지다. 한편, 실시 예에 따라, 애노드 전극(1)과 캐소드 전극(2) 중 어느 하나가 공통 전극으로 구현될 수도 있을 것이다.

- [0056] 도 4a에서는 발광 소자(200-1 내지 200-3)가 플립 칩(flip chip) 타입의 마이크로 LED인 것을 예로 들어 도시하였다. 그러나, 이에 한정되는 것은 아니며, 실시 예에 따라 발광 소자(200-1 내지 200-3)는 수평(lateral) 타입이나 수직(vertical) 타입의 마이크로 LED가 될 수도 있다.

- [0057] 구동 회로층(300)에는 전술한 바와 같이, 제 1 구동 회로(300-1)을 구동하기 위한 제 2 구동 회로(300-2)가 더 포함될 수 있다. 제 2 구동 회로(300-2)의 구체적인 내용에 관하여는 이후에 자세히 설명하기로 한다.

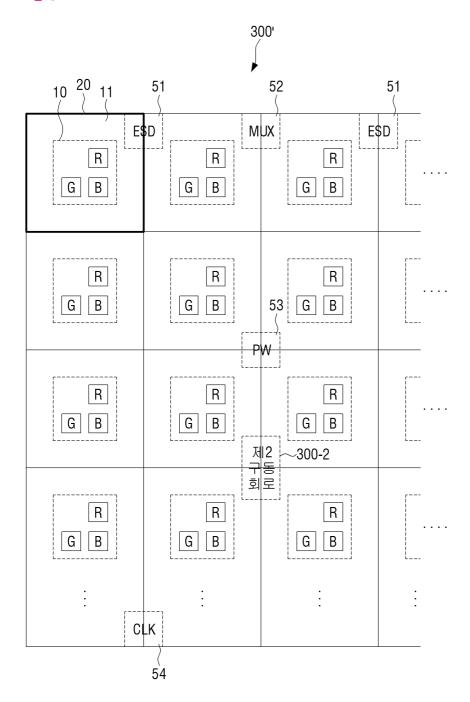

- [0058] 도 4b는 본 개시의 일 실시 예에 따른 구동 회로층(300)의 평면도이다. 구체적으로, 4b는 디스플레이 패널 (1000)의 구동 회로층(300)에 제 1 구동 회로(300-1) 및 제 2 구동 회로(300-2)가 배치되는 일 예를 도시하고 있다.

- [0059] 도 4b를 참조하면, 구동 회로층(300)에서 하나의 픽셀이 차지하는 전체 픽셀 영역(20)은, R, G, B 서브 픽셀을 각각 구동하기 위한 3개의 제 1 구동 회로(300-1)가 배치되는 영역(10) 및 주변의 나머지 영역(11)을 포함하는 것을 볼 수 있다. 이때, 본 개시의 일 실시 예에 따르면, R, G, B 서브 픽셀 각각에 대한 제 1 구동 회로(300-1)가 차지하는 영역(10)의 크기는, 전체 픽셀 영역(20)의 1/4 정도의 크기일 수 있으나, 이에 한정되는 것은 아니다.

- [0060] 이와 같이, 하나의 픽셀 영역(20)에는 나머지 영역(11)이 존재하며, 이는 다른 픽셀들도 마찬가지이다. 즉, 본 개시의 일 실시 예에 따르면, 구동 회로층(300)에는 제 1 구동 회로(300-1)가 차지하는 영역 외에 많은 공간이 존재하므로, 구동 회로층(300)의 나머지 영역(11)들에는, 도 4b에 도시된 바와 같이, 제 2 구동 회로(300-2)가 TFT로 형성되어 포함될 수 있다. 한편, 도 4b에 도시된 제 2 구동 회로(300-2)의 위치나 크기 및 개수는 하나의 예에 불과할 뿐, 도시된 바에 한정되는 것은 아니다.

- [0061] 한편, 본 개시의 일 실시 예에 따르면, 디스플레이 패널(1000)은, 픽셀(10)을 구성하는 복수의 서브 픽셀(10-1 내지 10-3) 중 어느 하나를 선택하기 위한 먹스(MUX) 회로, 디스플레이 패널(1000)에서 발생하는 정전기를 방지하기 위한 ESD(Electro Static Discharge) 회로, 구동 회로(300)에 전원을 공급하기 위한 전원 회로, 구동 회로(300)를 구동하는 클럭을 제공하기 위한 클럭 제공 회로, 매트릭스 형태로 배치된 디스플레이 패널(1000)의 각각의 픽셀 또는 각각의 서브 픽셀에 데이터 전압(예를 들어, 진폭 설정 전압 또는 펄스 폭 설정 전압 등)을 제공하기 위한 데이터 드라이버(또는 소스 드라이버) 등과 같은 각종 회로를 더 포함할 수 있다.

- [0062] 이하에서 도 5a 및 도 5b를 참조하여 이러한 각종 회로를 더 포함하는 디스플레이 패널의 예를 보다 구체적으로 설명하기로 한다. 도 5a 및 도 5b를 설명함에 있어 전술한 것과 중복되는 설명은 생략한다.

- [0063] 도 5a는 본 개시의 다른 일 실시 예에 따른 디스플레이 패널(1000')의 단면도이다. 도 5a에 도시된 바와 같이, 디스플레이 패널(1000')은, 글래스(100) 상에 형성되며 제 1 구동 회로(300-1) 및 제 2 구동 회로(300-2)를 포함하는 구동 회로층(300'), 구동 회로층(300') 상에 형성되어 디스플레이 패널(1000')의 서브 픽셀을 구성하는 발광 소자(200-1 내지 200-3), 상술한 각종 회로(400), 구동 회로층(300')과 상술한 각종 회로(400)를 전기적으

로 연결하는 연결 배선(500)을 포함할 수 있다.

- [0064] 구동 회로층(300')은 TFT로 구현된 제 1 및 제 2 구동 회로(300-1, 300-2)를 포함하며, 글래스(100)의 일면 상에 형성된다. 상술한 각종 회로(400)는 글래스(100)의 타 면에 구동 회로층(300')과는 별도의 반도체 IC로 형성내지 배치될 수 있다.

- [0065] 이때, 본 개시의 일 실시 예에 따르면, 디스플레이 패널(1000')은 TFT 기판의 에지 영역에 연결 배선(500)을 형성하여, 글래스(100)의 일 면에 형성된 구동 회로층(300')과 글래스(100)의 타 면에 형성된 각종 회로(400)를 전기적으로 연결할 수 있다.

- [0066] 이와 같이, TFT 기판의 에지 영역에 연결 배선(500)을 형성하는 이유는, 글래스(100)를 관통하는 홀(Hole)을 형성하여 글래스(100) 양면에 배치된 회로들을 서로 연결하는 경우, TFT 기판의 제조 공정과 홀에 전도성 물질을 채우는 공정 간의 온도 차이로 인해 글래스에 크랙이 생기는 등과 같은 문제가 발생할 수 있기 때문이다.

- [0067] 한편, 이상에서는, 상술한 각종 회로들이 모두, 참조 부호 400과 같이, 구동 회로층(300')이 형성되는 글래스 (100) 면의 반대 면에 별도로 형성되는 것을 예로 들었으나, 실시 예가 이에 한정되는 것은 아니다. 즉, 각종 회로들의 전/일부는 구동 회로층(300')에 포함되어 형성될 수 있다.

- [0068] 예를 들어, 전술한 각종 회로들이 모두 구동 회로층(300')에 형성될 수도 있는데, 이 경우에는, 글래스(100)의 상기 타 면에 별도로 회로가 배치될 필요가 없으므로, 글래스(100)의 전, 후면을 연결하는 도 5a의 연결 배선 (500)도 필요가 없게 될 것이다.

- [0069] 또한, 다른 예로, 먹스 회로, ESD 회로, 전원 회로, 클럭 제공 회로는 TFT로 구현되어 구동 회로층(300')에 포함되고, 데이터 드라이버 회로는 글래스(100)의 상기 타 면에 별도로 배치되도록 디스플레이 패널이 구현될 수도 있다. 도 5b는 이러한 실시 예를 도시하고 있다.

- [0070] 도 5b는 본 개시의 다른 일 실시 예에 따른 구동 회로층(300')의 평면도이다. 구체적으로, 5b는 디스플레이 패널(1000')의 구동 회로층(300')에 포함된 각종 회로의 배치를 도시하고 있다.

- [0071] 도 4b에서 전술한 바와 같이, 구동 회로층(300')에는 제 1 구동 회로(300-1)가 차지하는 영역(10) 외에 많은 공간이 존재하므로, 구동 회로층(300')의 나머지 영역(11)들에는, 제 2 구동 회로(300-2) 외에도, 도 5b에 도시된바와 같이, ESD 회로(51), MUX 회로(52), 전원 회로(53), 클럭 제공 회로(54)가 TFT로 구현되어 포함될 수있다. 이 경우, 데이터 드라이버 회로는, 글래스(100)의 상기 타 면에 도 5a의 참조 부호 400과 같이 배치되게될 것이다. 한편, 도 5b에 도시된 ESD 회로(51), MUX 회로(52), 전원 회로(53), 클럭 제공 회로(54)의 위치나크기 및 개수는 하나의 예에 불과할 뿐, 도시된 바에 한정되는 것은 아니다.

- [0072] 한편, 각종 회로들이 글래스(100)를 중심으로 양면에 나뉘어 배치되는 실시 예가 도 5b의 예에 한정되는 것이 아님은 물론이며, 도 5b의 ESD 회로(51), MUX 회로(52), 전원 회로(53), 클럭 제공 회로(54) 중 적어도 하나의 회로가 상기 글래스(100)의 타 면에 도 5a의 참조 부호 400과 같이 배치될 수도 있음은 물론이다.

- [0073] 한편, 이상에서는, 제 2 구동 회로(300-2)가 구동 회로층(300, 300')에 포함된 것을 예로 들어 설명하였으나, 반드시 이에 한정되는 것은 아니며, 실시 예에 따라 제 2 구동 회로(300-2)가 상기 글래스(100)의 타 면에 도 5a의 참조 부호 400과 같이 배치되는 실시 예도 가능하다.

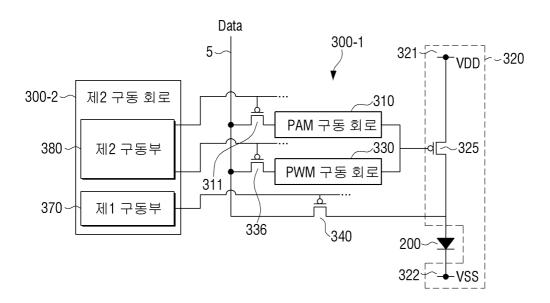

- [0074] 도 6은 본 개시의 일 실시 예에 따른 디스플레이 패널(1000, 1000')에 포함된 하나의 서브 픽셀과 관련된 구성을 도시한 구성도이다. 도 6에 따르면, 디스플레이 패널(1000, 1000')은 발광 소자(200), 제 1 구동 회로(300-1) 및 제 2 구동 회로(300-2)를 포함한다.

- [0075] 제 1 구동 회로(300-1)는 PAM(Pulse Amplitude Modulation) 구동 회로(310), PWM(Pulse Width Modulation) 구동 회로(330), 전류원(320), 제 1 트랜지스터(340)를 포함한다.

- [0076] 전류원(320)은 발광 소자(200)로 구동 전류를 제공한다. 구체적으로, 전류원(320)은 구동 전압 단자(321)와 그라운드 전압 단자(322) 사이에 연결된 구동 트랜지스터(325)를 포함한다.

- [0077] PAM 구동 회로(310)는 발광 소자(200)로 제공되는 구동 전류의 진폭을 제어할 수 있다. 특히, PAM 구동 회로 (310)는, 데이터 라인(5)과 연결된 제 2 트랜지스터(311)를 포함하고, 제 2 트랜지스터(311)를 통해 입력되며 외부로 제공된 전류에 기초하여 보정되는 진폭 설정 전압에 따라 발광 소자(200)를 PAM 제어할 수 있다.

- [0078] 이를 위해, 제 1 구동 회로(300-1)는 제 1 트랜지스터(340)를 포함할 수 있다.

- [0079] 구체적으로, 제 1 트랜지스터(340)는 데이터 라인(5)과 전류원(320)(구체적으로는, 구동 트랜지스터(325)의 드 레인 단자) 사이에 연결되어, 전류원(320)(구체적으로는, 구동 트랜지스터(325))을 흐르는 전류를 데이터 라인(5)을 통해 외부로 제공할 수 있다. 이와 같이 데이터 라인(5)으로 전달된 전류는 데이터 라인(5)을 통해 제 1 구동 회로(300-1) 외부의 전류 검출부(미도시)에 의해 검출될 수 있으며, 제 1 구동 회로(300-1) 외부의 프로세서 또는 TCON(Timing Controller)(미도시)은, 위와 같이 검출된 전류에 기초하여 진폭 설정 전압을 보정하고, 보정된 진폭 설정 전압을 PAM 구동 회로(310)에 인가할 수 있다.

- [0080] 이에 따라, 디스플레이 패널(1000)의 각 서브 픽셀을 구성하는 복수의 제 1 구동 회로(300-1)들 간의 편차(구체 적으로는, 구동 트랜지스터(325)들 간의 문턱전압 편차)로 인해 발생하는 구동 전류의 진폭 편차가 보상될 수 있다.

- [0081] 한편, PWM 구동 회로(330)는 데이터 라인(5)과 연결된 제 3 트랜지스터(336)를 포함하고, 제 3 트랜지스터(336)를 통해 입력되는 펄스 폭 설정 전압에 기초하여 발광 소자(200)를 PWM 제어할 수 있다.

- [0082] 이때, 도 6에서는 도시하지 않았지만, PWM 구동 회로(330)는 일명 "다이오드 커넥티드 방식"으로 연결된 2개의 트랜지스터를 포함할 수 있다. 구체적으로, PWM 구동 회로(330)는 제 4 트랜지스터(도 7의 331) 및 제 4 트랜지스터(331)의 게이트 단자와 드레인 단자 사이에 연결된 제 5 트랜지스터(도 7의 332)를 포함할 수 있다.

- [0083] 따라서, PWM 구동 회로(330)는 동작 과정에서 제 4 트랜지스터(331)의 문턱전압이 반영된 전압이 제 4 트랜지스터(331)의 게이트 단자에 인가될 수 있다.

- [0084] 이에 따라, 디스플레이 패널(1000)의 각 서브 픽셀을 구성하는 복수의 제 1 구동 회로(300-1)들 간의 편차(구체 적으로는, 제 4 트랜지스터(도 7의 331)들 간의 문턱전압 편차)로 인해 발생하는 구동 전류의 펄스 폭 편차가 보상될 수 있다.

- [0085] 한편, 도 6에는 제 2 구동 회로(300-2)와 제 1 구동 회로(300-1)의 연결 관계를 도시하기 위해, 편의상 제 1 구동 회로(300-1)만을 도시하였다. 그러나, 제 2 구동 회로(300-2)는 전술한 바와 같이, 디스플레이 패널(1000, 1000')에 포함된 복수의 픽셀을 라인별로 제어하므로, 해당 라인에 포함된 모든 픽셀의 제 1 구동 회로들과 연결될 수 있음은 물론이다.

- [0086] 구체적으로, 본 개시의 일 실시 예에 따르면, 제 2 구동 회로(300-2)의 제 1 구동부(370)는 디스플레이 패널 (1000, 1000')의 복수의 가로 라인 중 하나의 라인의 복수의 픽셀을 구성하는 발광 소자들을 구동하기 위한 복수의 제 1 구동 회로(300-1)에 포함된 제 1 트랜지스터들(340)을 온 시키기 위한 제 1 제어 신호를 영상 프레임 별로 생성하고, 생성된 제 1 제어 신호를 상기 하나의 라인의 제 1 트랜지스터(340)들로 제공할 수 있다.

- [0087] 이를 위해, 제 1 구동부(370)는, 하나의 영상 프레임에 대해, 하나의 라인의 제 1 트랜지스터들(340)을 온 시키기 위한 제어 신호를 생성하고, 상기 하나의 영상 프레임의 다음 영상 프레임에 대해, 상기 하나의 라인 다음의라인의 제 1 트랜지스터들(300-1)을 온 시키기 위한 제어 신호를 생성할 수 있다.

- [0088] 또한, 제 2 구동부(380)는, 디스플레이 패널(1000, 1000')의 복수의 제 1 구동 회로(300-1)들에 포함된 제 2 트랜지스터들(311) 및 제 3 트랜지스터들(336)을, 하나의 영상 프레임에 대해 라인 별로 온 시키기 위한 제 2 및 제 3 제어 신호를 생성하고, 상기 생성된 제 2 및 제 3 제어 신호를 상기 각 라인의 상기 제 2 트랜지스터들(311) 및 제 3 트랜지스터들(336)로 제공할 수 있다.

- [0089] 이하에서는, 도 7 내지 도 9를 통해 상술한 본 개시의 다양한 실시 예들에 따른 제 1 구동 회로(300-1)의 동작에 대해 보다 자세히 설명한다.

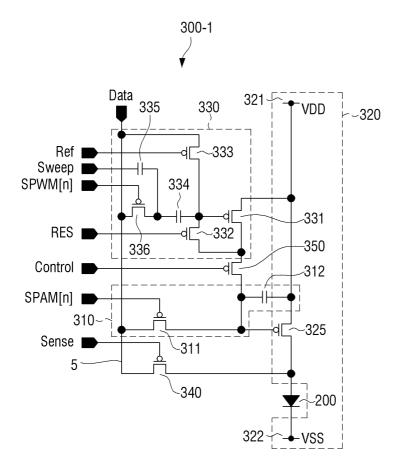

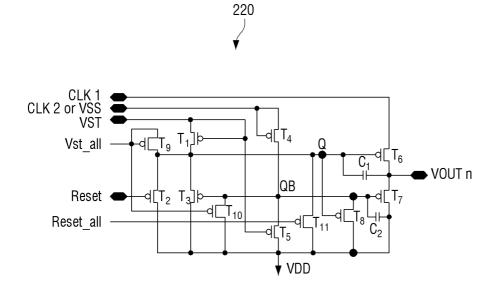

- [0090] 도 7은 본 개시의 일 실시 예에 따른 제 1 구동 회로(300-1)의 상세 회로도이다. 도 7에 따르면, 제 1 구동 회로(300-1)는 PAM 구동 회로(310), 전류원(320), PWM 구동 회로(330), 제 1 트랜지스터(340) 및 제 7 트랜지스터(350)를 포함할 수 있다.

- [0091] 한편, 도 7에 도시된 제 1 구동 회로(300-1)는 하나의 발광 소자(200)를 구동하기 위한 회로이며, 전술한 바와 같이, 디스플레이 패널(1000, 1000')에 마련된 복수의 픽셀 각각은 복수의 발광 소자를 포함한다는 점에서, 디스플레이 패널(1000, 1000')에는 도 7과 같은 제 1 구동 회로(300-1)가 복수 개 마련될 수 있다.

- [0092] PAM 구동 회로(310)는 데이터 라인(5)을 통해 입력되는 전압을 전류원(320)의 구동 트랜지스터(325)의 게이트 단자에 인가할 수 있다. 이를 위해, PAM 구동 회로(310)는 소스 단자가 데이터 라인(5)에 연결되고, 드레인 단자가 구동 트랜지스터(325)의 게이트 단자에 연결되는 제 2 트랜지스터(311) 및 일 단이 구동 트랜지스터(325)

의 소스 단자에 연결되고, 타 단이 구동 트랜지스터(325)의 게이트 단자 및 제 2 트랜지스터(311)의 드레인 단자와 공통 연결되는 제 1 커패시터(312)를 포함할 수 있다.

- [0093] 따라서, PAM 구동 회로(310)는 제어 신호(SPAM(n))에 따라 제 2 트랜지스터(311)가 온된 동안 데이터 라인(5)을 통해 진폭 설정 전압(PAM data)이 입력되면, 입력된 진폭 설정 전압을 제 1 커패시터(312)에 충전시키고, 제 1 커패시터(312)에 충전된 전압을 구동 트랜지스터(325)의 게이트 단자에 인가할 수 있다.

- [0094] 한편, 도 7에 도시된 바와 같이, 구동 트랜지스터(325)의 소스 단자는, 제 1 커패시터(312)의 일단 및 제 1 구동 회로(300-1)의 구동 전압 단자(321)에 공통 연결되고, 구동 트랜지스터(325)의 드레인 단자는, 발광 소자 (200)의 애노드 단자와 연결되며, 발광 소자(200)의 캐소드 단자는, 제 1 구동 회로(300-1)의 그라운드 전압 단자(322)에 연결될 수 있다.

- [0095] 이에 따라, 전류원(320)은, 구동 전압 단자(321)에 구동 전압(VDD)이 인가되고 제 1 커패시터(312)에 충전된 전압이 구동 트랜지스터(325)의 게이트 단자에 인가된 상태에서, 그라운드 전압 단자(322)의 전압이 그라운드 전압(VSS)이 되면, 제 1 커패시터(312)에 충전된 전압의 크기에 대응되는 진폭의 구동 전류를 발광 소자(200)로 제공할 수 있다.

- [0096] 제 7 트랜지스터(350)는 드레인 단자가 구동 트랜지스터(325)의 게이트 단자와 연결되고, 소스 단자가 제 4 트랜지스터(331) 및 제 5 트랜지스터(332)의 드레인 단자와 공통 연결되며, 제어 신호(Control)에 따라 PAM 구동 회로(310)와 PWM 구동 회로(330)를 전기적으로 연결 또는 분리한다.

- [0097] 한편, PWM 구동 회로(330)는 데이터 라인(5)을 통해 구동 전류의 펄스 폭을 결정하는 펄스 폭 설정 전압이 인가되면, 펄스 폭 설정 전압에 기초하여 구동 트랜지스터(325)의 게이트 단자 전압을 제어할 수 있다.

- [0098] 이를 위해, PWM 구동 회로(330)는 제 4 트랜지스터(331), 제 4 트랜지스터(331)의 게이트 단자와 드레인 단자 사이에 연결된 제 5 트랜지스터(332), 소스 단자가 데이터 라인(5)에 연결되고 드레인 단자가 제 4 트랜지스터 (331)의 게이트 단자 및 제 5 트랜지스터(332)의 소스 단자와 공통 연결되는 제 6 트랜지스터(333), 일 단이 제 4 트랜지스터(331)의 게이트 단자, 제 5 트랜지스터(332)의 소스 단자 및 제 6 트랜지스터(333)의 드레인 단자와 공통 연결되는 제 2 커패시터(334), 일 단이 스위프 신호를 입력받고 타 단이 제 2 커패시터(334)의 타 단과연결되는 제 3 커패시터(335) 및 소스 단자가 데이터 라인(5)과 연결되고, 드레인 단자가 제 2 커패시터(334)의상기 타 단 및 제 3 커패시터(335)의 상기 타 단과 공통 연결되는 제 3 트랜지스터(336)를 포함할 수 있다. 여기에서, 구동 트랜지스터(325)의 게이트 단자와 제 4 트랜지스터(331)의 드레인 단자 사이에는 제 7 트랜지스터 (350)가 연결될 수 있다.

- [0099] 이에 따라, 제 4 트랜지스터(331)의 게이트 단자 전압은, 제 5 트랜지스터(332)가 온된 동안 제 4 트랜지스터 (331)의 문턱 전압에 기초한 전압으로 세팅된다. 이후, 제어 신호(SPWM(n))에 따라 제 3 트랜지스터(336)가 온된 동안 데이터 라인(5)을 통해 펄스 폭 설정 전압(PWM data)이 입력되면, 제 4 트랜지스터(331)의 게이트 단자 전압은, 제 4 트랜지스터(331)의 문턱 전압 및 펄스 폭 설정 전압에 기초한 전압으로 세팅되고, 이후 제 3 커패 시터(335)의 일 단을 통해 선형 변화하는 스위프 신호가 입력되면, 제 4 트랜지스터(331)의 게이트 단자 전압은 스위프 신호에 따라 선형 변화된다.

- [0100] 선형 변화되는 제 4 트랜지스터(331)의 게이트 단자 전압이 제 4 트랜지스터(331)의 문턱 전압에 도달하면 제 4 트랜지스터(331)는 온되고, 제 4 트랜지스터(331)의 소스 단자에 인가되고 있는 구동 전압(VDD)은 제 4 트랜지스터(331)의 드레인 단자를 통해 구동 트랜지스터(325)의 게이트 단자에 인가되게 된다(이때, 제 7 트랜지스터(350)가 온된 상태여야 함은 물론이다.). 이에 따라, 구동 트랜지스터(325)는 오프되며, 발광 소자(200)를 흐르던 구동 전류는 멈추게 되어 발광 소자(200)의 발광 시간이 제어되게 된다.

- [0101] 이때, 스위프 신호의 선형 변화 기울기는 디스플레이 패널(1000, 1000')을 구성하는 모든 제 1 구동 회로(300-1)에 대해 동일하고, 제 4 트랜지스터(331)의 게이트 단자 전압은, 스위프 신호 입력에 따라 제 4 트랜지스터(331)의 문턱 전압 및 펄스 폭 설정 전압에 기초한 전압부터 선형적으로 변환하게 된다.

- [0102] 따라서, 스위프 신호 인가 후 제 4 트랜지스터(331)의 게이트 단자 전압이 제 4 트랜지스터(331)의 문턱 전압에 도달하는 시간은 펄스 폭 설정 전압의 크기에 따라 달라지므로, PWM 구동 회로(330)는 펄스 폭 설정 전압의 크기에 따라 다양한 계조 표현을 할 수 있다.

- [0103] 또한, 구동 트랜지스터(325)를 흐르는 구동 전류의 구동 시간은, 제 4 트랜지스터(331)의 게이트 단자 전압이, 스위프 신호 입력에 따라 제 4 구동 트랜지스터(331)의 문턱 전압 및 펄스 폭 설정 전압에 기초한 전압부터 선

형 변화하여 제 4 트랜지스터(331)의 문턱 전압에 도달할 때까지가 되므로, 제 4 트랜지스터(331)의 문턱 전압과 무관하게 결정된다. 따라서, 본 개시의 일 실시 예에 따르면, 디스플레이 패널(1000, 1000')의 복수의 픽셀을 구성하는 복수의 제 1 구동 회로(300-1) 각각에 포함된 제 4 트랜지스터(331)들 간의 문턱 전압 편차를 보상할 수 있다.

- [0104] 한편, 도 7에 도시된 바와 같이, 본 개시의 다양한 실시 예들에 따른 디스플레이 패널(1000, 1000')은, 각 서브 픽셀을 구동하기 위한 제 1 구동 회로(300-1)가 TFT로 구현된 AM(Active Matrix) 구동 방식의 디스플레이 패널 인 것을 알 수 있다.

- [0105] 도 8은 디스플레이 패널에 포함된 제 1 구동 회로(300-1)를 구동하기 위한 각종 신호의 타이밍도이다. 한편, 도 8에 도시된 각종 전압이나 시간에 관한 수치는 하나의 실시 예에 불과하며, 해당 값에 한정되는 것은 아니다.

- [0106] 도 8을 참조하면, 제 1 구동 회로(300-1)는, 하나의 영상 프레임을 디스플레이하는 동안, 센싱 기간(duration), 리셋 기간, 데이터 전압 설정 기간 및 발광 기간 순으로 구동될 수 있다.

- [0107] 센싱 기간은 구동 트랜지스터(325)를 흐르는 전류를 감지하기 위한 기간이다. 센싱 기간은 특정 전압을 구동 트랜지스터(325)의 게이트 단자에 인가하기 위한 전압 설정 기간과 특정 전압에 대응되는 구동 트랜지스터(325)를 흐르는 전류를 감지하기 위한 전류 감지 기간을 포함할 수 있다.

- [0108] 이때, 특정 전압은 발광 소자(200)로 제공되는 구동 전류의 진폭을 결정하는 진폭 설정 전압과는 다른 전압으로, 특정 전압에 대응되는 구동 트랜지스터(325)를 흐르는 전류를 감지하여 복수의 화소 구동 회로 각각에 포함된 구동 트랜지스터(325)들 간의 문턱전압 편차를 보정하기 위한 전압이다.

- [0109] 구체적으로, 전압 설정 기간 내에 제어 신호(SPAM(n))에 따라 제 2 트랜지스터(311)가 온되면, 데이터 라인(5)을 통해 특정 전압이 제 1 커페시터(312)에 충전된다. 이후, 전류 감지 기간 내에 제어 신호(Sense)에 따라 제 1 트랜지스터(340)가 온되면, 구동 트랜지스터(325)를 흐르는 특정 전압에 대응되는 전류가 제 1 트랜지스터(340)를 통해 데이터 라인(5)으로 전달된다.

- [0110] 한편, 특정 전압은 실시 예에 따라 다양하게 설정될 수 있다. 예를 들어, 디스플레이 패널이 일반적으로 구동될 때의 구동 전류(즉, 티파컬 전류)를 감지하기 위한 특정 전압과 디스플레이 패널이 최대 밝기로 구동될 때의 구동 전류(즉, 피크 전류)를 감지하기 위한 특정 전압은 서로 다를 수 있고, 필요에 따라 다른 크기의 특정 전압이 전압 설정 기간에 데이터 라인(5)을 통해 인가될 수 있다.

- [0111] 이와 같이 데이터 라인(5)으로 전달된 전류는 제 1 구동 회로(300-1) 외부의 전류 검출부(미도시)에 의해 검출될 수 있다. 따라서, 본 개시의 일 실시 예에 따르면, 제 1 구동 회로(300-1) 외부의 프로세서 또는 TCON(Timing Controller)(미도시)은, 위와 같이 검출된 전류에 기초하여 진폭 설정 전압을 보정하고, 보정된 진폭 설정 전압을 데이터 전압 설정 기간에 PAM 구동 회로(310)에 인가할 수 있으며, 이에 따라, 디스플레이 패널을 구성하는 복수의 제 1 구동 회로(300-1) 각각에 포함된 구동 트랜지스터(325)들 간의 문턱전압 편차가 보상될 수 있다.

- [0112] 예를 들어, 전압 설정 기간에 구동 트랜지스터(325)의 게이트 단자에 인가한 특정 전압이 a이고, 감지된 전류의 크기가 x인 경우, 프로세서 또는 TCON(Timing Controller)(미도시)은, 특정 전압과 전류의 크기값이 매핑되어 있는 기저장된 테이블에서 전압 a에 대응되는 전류의 크기(예를 들어, y)를 확인할 수 있다. 이에 따라, 만일 x 가 y보다 큰 경우, 즉, 감지된 전류가 테이블에 따른 전류보다 큰 경우, 프로세서 또는 TCON(Timing Controller)(미도시)은, 이후 데이터 전압 설정 기간에 구동 트랜지스터(325)에 인가할 진폭 설정 전압을 보다 낮게 보정할 수 있다. 만일, x가 y보다 작은 경우라면, 진폭 설정 전압은 보다 높은 값을 갖도록 보정되어 PAM 구동 회로(310)로 인가되게 될 것이다. 이에 따라, 디스플레이 패널의 복수의 픽셀을 구성하는 복수의 제 1 구동 회로(300-1) 각각에 포함된 구동 트랜지스터(325)들 간의 문턱전압 편차가 보상될 수 있다.

- [0113] 리셋 기간은 제 4 트랜지스터(331)의 게이트 단자 전압을 제 4 트랜지스터(331)의 문턱 전압에 기초한 전압으로 세팅하기 위한 기간이다. 이때, 리셋 기간은 구동 회로(300-1)의 제 4 트랜지스터(331)의 게이트 단자 전압 및/또는 구동 트랜지스터(325)의 게이트 단자 전압을 기설정된 레퍼런스 전압으로 세팅하기 위한 초기화 기간 및제 4 트랜지스터(331)의 게이트 단자 전압을 제 4 트랜지스터(331)의 문턱 전압에 기초한 전압으로 세팅하기 위한 문턱 전압 세팅 기간을 포함할 수 있다.

- [0114] 구체적으로, 리셋 기간이 시작되면, 제어 신호(RES)에 따라 제 5 트랜지스터(332)가 온된다. 이때, 제 5 트랜지스터(332)가 온된 동안 제어 신호(Ref)에 따라 제 6 트랜지스터(333)가 온/오프된다. 구체적으로, 제 6 트랜지

스터(333)는 도 8에 도시된 바와 같이, 초기화 기간 동안 온된 후 오프될 수 있다.

- [0115] 제 6 트랜지스터(333)가 온되면, 기설정된 레퍼런스 전압(도 8의 예에서는 0V 내지 4V)이 데이터 라인(5)을 통해 제 4 트랜지스터(331)의 게이트 단자에 인가되므로, 제 4 트랜지스터(331)의 게이트 단자 전압은, 제 6 트랜지스터(333)가 온된 동안 레퍼런스 전압으로 세팅된다.

- [0116] 이후, 문턱 전압 세팅 기간이 시작되면, 제 6 트랜지스터(333)는 오프되는데, 이에 따라, 제 4 트랜지스터(33 1)의 게이트 단자 전압은, 구동 전압(VDD)과 제 4 트랜지스터(331)의 문턱전압(Vth)의 합에 해당하는 전압으로 세팅되게 된다.

- [0117] 한편, 도 8을 참조하면, 제어 신호(Control)에 따라 제 6 트랜지스터(333)가 온된 동안 제 7 트랜지스터(350)가 온되므로, 제 4 트랜지스터(331)의 게이트 단자에 인가된 레퍼런스 전압은 구동 트랜지스터(325)의 게이트 단자에 그대로 동일하게 인가된다. 즉, 초기화 기간 동안, 제 4 트랜지스터(331)의 게이트 단자 전압 및 구동 트랜지스터(325)의 게이트 단자 전압은 모두 기설정된 레퍼런스 전압(예를 들어, 0V)으로 세팅된다.

- [0118] 이와 같이, 문턱 전압 세팅 기간 전에 제 4 트랜지스터(331)의 게이트 단자 전압 및 구동 트랜지스터(325)의 게이트 단자 전압을 레퍼런스 전압으로 명확히 세팅함으로써, 제 4 트랜지스터(331)의 게이트 단자 전압의 플로팅으로 인한 부정확한 동작을 방지할 수 있다.

- [0119] 데이터 전압 설정 기간은 펄스 폭 설정 전압(PWM data) 및 진폭 설정 전압(PAM data)을 PWM 구동 회로(330) 및 PAM 구동 회로(310)에 각각 인가하기 위한 기간이다.

- [0120] 구체적으로, 데이터 전압 설정 기간 동안, 제어 신호(SPWM(n))에 따라 제 3 트랜지스터(336)가 온되면, 데이터 라인(5)을 통해 인가되는 펄스 폭 설정 전압이 제 2 캐패시터(334)를 통해 제 4 트랜지스터(331)의 게이트 단자에 인가된다. 이에 따라, 제 4 트랜지스터(331)의 게이트 단자 전압은, 펄스 폭 설정 전압(Vw)만큼 상승되며, 상승된 전압은 제 2 커패시터(334)에 의해 유지된다.

- [0121] 한편, 데이터 전압 설정 기간 동안, 제어 신호(SAWM(n))에 따라 제 2 트랜지스터(311)가 온되면, 데이터 라인 (5)을 통해 인가되는 진폭 설정 전압이 제 1 커패시터(312)에 충전되어 유지된다. 이때, 데이터 라인(5)을 통해 인가되는 진폭 설정 전압은, 센싱 기간 동안 감지된 구동 트랜지스터(325)를 흐르는 전류에 기초하여 보정된 전압일 수 있다.

- [0122] 한편, 도 8에서는, PWM Data 즉, 펄스 폭 설정 전압이 먼저 인가되고, 이후에 PAM Data 즉, 진폭 설정 전압이 인가되는 것을 예로 들었으나 이에 한정되는 것은 아니며, 실시 예에 따라 PAM Data가 먼저 인가된 후 PWM Data가 인가될 수도 있다.

- [0123] 발광 기간은 펄스 폭 설정 전압 및 진폭 설정 전압에 따라 발광 소자(200)가 발광하는 기간이다. 구체적으로, 도 8에 도시된 바와 같이, 발광 기간이 시작되면, 제 1 구동 회로(300-1)의 그라운드 전압 단자(322)의 전압은 그라운드 전압(VSS, 예를 들어 0V)로 떨어지며, 이에 따라, 구동 트랜지스터(325)가 온되어 제 1 커패시터(31 2)에 충전된 진폭 설정 전압에 대응되는 진폭을 갖는 구동 전류가 발광 소자(200)로 제공된다. 이에 따라, 발광소자(200)는 발광을 시작한다.

- [0124] 한편, 발광 기간이 시작되면, 제 3 커패시터(335)를 통해 제 2 커패시터(334)의 일단에 스위프 전압이 인가되므로, 제 2 커패시터(334)의 타 단에 연결되어 있는 제 4 트랜지스터(331)의 게이트 단자 전압 역시, 유지되던 전압(VDD + Vth + Vw)부터 스위프 전압에 따라 선형 감소하게 된다.

- [0125] 선형 감소하던 제 4 트랜지스터(331)의 게이트 단자 전압이 제 2 트랜지스터(331)의 문턱전압(Vth)에 도달하면, 제 4 트랜지스터(331)는 온되며, 제 7 트랜지스터(350)를 통해 구동 트랜지스터(325)의 게이트 단자 전압에 구동 전압(VDD)이 인가된다. 이에 따라, 구동 트랜지스터(325)가 오프되면, 구동 전류는 차단되고, 발광 소자 (200)는 발광을 멈추게 된다.

- [0126] 즉, 발광 소자(200)는, 발광 기간이 시작하는 시점부터 제 4 트랜지스터(331)의 게이트 단자 전압이 스위프 전압에 따라 선형 감소하여 제 4 트랜지스터(331)의 문턱전압(Vth)에 도달할 때까지 발광하게 된다.

- [0127] 다시 도 8을 참조하면, 도 8은 디스플레이 패널(1000, 1000')에서 복수의 픽셀이 270개의 가로 라인으로 구성되는 실시 예를 도시하고 있다. 따라서, 도 8에 도시된 바와 같이, 제어 신호 SPWM 및 SPAM이, 데이터 전압 설정기간에, SPWM 1부터 SPWM 270까지, 그리고, SPAM 1부터 SPAM 270까지 각각 순차 구동되는 것을 볼 수 있다.

- [0128] 한편, 본 개시의 일 실시 예에 따르면, 디스플레이 패널(1000, 1000')의 각 픽셀을 구성하는 R, G, B 서브 픽셀

은 하나의 데이터 라인(5)과 연결된 구조를 가질 수 있다. 이때, R, G, B 서브 픽셀은, 먹스(Multiplexer, Mu x)를 통해, 하나의 데이터 라인(5)을 통해 인가되는 서로 다른 데이터 전압을 입력받을 수 있다.

- [0129] 따라서, 도 8에 도시된 바와 같이, 디스플레이 패널(1000, 1000')의 각 픽셀을 구성하는 R, G, B 서브 픽셀은, 데이터 전압 설정 기간에 먹스를 통해 시분할 구동(또는, 순차적으로 선택)되어 서로 다른 크기의 펼스 폭 설정 전압 또는 진폭 설정 전압을 데이터 라인(5)으로부터 입력받을 수 있다.

- [0130] 이와 같은 동작은 센싱 기간에서도 마찬가지인데, 도 8에 도시된 바와 같이, 본 개시의 일 실시 예에 따르면, 디스플레이 패널(1000, 1000')의 각 픽셀을 구성하는 R, G, B 서브 픽셀은, 전압 설정 기간에 먹스를 통해 순차적으로 선택되어 서로 다른 크기의 특정 전압을 데이터 라인(5)으로부터 입력받을 수 있다. 이때, R, G, B 서브 픽셀 각각에 입력되는 특정 전압은 서브 픽셀의 종류에 기초하여 이론적 또는 실험적으로 결정된 값일 수 있다. 실시 예에 따라 서로 다른 크기의 특정 전압이 R, G, B 서브 픽셀 각각에 입력되거나, 동일한 크기의 특정 전압이 R, G, B 서브 픽셀 각각에 입력될 수 있다.

- [0131] 또한, 디스플레이 패널(1000, 1000')은, 센싱 기간 동안 R, G, B 서브 픽셀에 대응되는 화소 구동 회로의 구동 트랜지스터(325)를 흐르는 전류를, 전류 감지 기간 내의 서로 다른 기간에 감지하도록 구동될 수 있다.

- [0132] 이때, 본 개시의 일 실시 예에 따르면, 디스플레이 패널(1000, 1000')은, 센싱 기간 동안, 복수의 픽셀 중 하나의 라인의 복수의 픽셀을 구성하는 복수의 발광 소자를 구동하기 위한 복수의 제 1 구동 회로(300-1)의 구동 트랜지스터(325)를 흐르는 전류를 감지하도록 구동될 수 있다. 즉, 디스플레이 패널(1000, 1000')은 하나의 영상 프레임에 대해, 하나의 가로 라인에 배치된 복수의 픽셀을 구성하는 복수의 발광 소자를 구동하기 위한 복수의 제 1 구동 회로(300-1)의 구동 트랜지스터들(325)을 흐르는 전류만을 감지하도록 구동될 수 있다. 즉, 디스플레이 패널(1000, 1000')은 영상 프레임별로, 하나의 라인에 포함된 구동 트랜지스터들(325)을 흐르는 전류를 감지하도록 구동될 수 있다. 이때, 디스플레이 패널(1000, 1000')은 영상 프레임마다 가로 라인을 순차적으로 변경하면서 해당 라인에 포함된 구동 트랜지스터들(325)을 흐르는 전류를 감지하도록 구동될 수 있다.

- [0133] 일반적으로 하나의 영상 프레임이 표시되는 시간은 시청자가 눈으로 인식할 수 없는 매우 짧은 시간이기 때문에, 위와 같이 하나의 영상 프레임에 하나의 가로 라인만을 센싱하더라도 구동 트랜지스터들(325) 간의 문턱 전압 편차를 보상하는데 충분할 수 있다.

- [0134] 다만, 실시 예가 이에 한정되는 것은 아니며, 디스플레이 패널(1000, 1000')은 하나의 영상 프레임에 대해 센싱 기간 동안 2개 이상의 가로 라인에 포함된 구동 트랜지스터들(325)을 흐르는 전류를 감지하도록 구동될 수도 있음은 물론이다.

- [0135] 이상에서는, 제 1 구동 회로(300-1)에 포함된 트랜지스터들(325, 350, 311, 331, 332, 333, 336, 340)이 모두 PMOSFET(P-channel Metal Oxide Semiconductor Field Effect Transistor)으로 구현된 것을 예로 들었다. 그러나, 실시 예가 이에 한정되는 것은 아니다. 즉, 본 개시의 일 실시 예에 따르면, 포함된 트랜지스터들이 모두 NMOSFET(N-channel Metal Oxide Semiconductor Field Effect Transistor)으로 구성된 제 1 구동 회로도 상술한 제 1 구동 회로(300-1)와 동일한 동작을 하도록 구현될 수 있다. 도 9는 이와 같이 제 1 구동 회로에 포함된 트랜지스터들이 모두 NMOSFET으로 구현된 제 1 구동 회로(900)를 도시하고 있다.

- [0136] 도 9의 제 1 구동 회로(900)는, 트랜지스터의 종류 차이로 인한 차이점(예를 들어, 소자들 간의 연결 관계 차이 및 인가되는 각종 신호의 극성 차이)을 제외하고는, 도 7 제 1 구동 회로(300-1)와 동일한 동작을 수행할 수 있다. 따라서, 도 9의 제 1 구동 회로(900)에서는 도 7의 제 1 구동 회로(300-1)에 포함된 소자들과 동일한 기능을 수행하는 소자들에 대해 동일한 참조 부호를 사용하였다. 당업자라면 이상의 설명을 통해 제 1 구동 회로(900)의 구성 및 동작을 용이하게 이해할 수 있으므로, 이하 불필요한 중복 설명은 생략한다.

- [0137] 한편, 전술한 바와 같이, 본 개시의 일 실시 예에 따르면, 디스플레이 패널(1000, 1000')은 영상 프레임마다 가로 라인이 순차적으로 변경되면서 변경된 가로 라인에 포함된 구동 트랜지스터들을 흐르는 전류를 감지하도록 구동될 수 있다. 이를 위해서는, 영상 프레임마다 가로 라인을 순차적으로 변경하면서 센싱 기간에 제어 신호 (Sense)가 변경된 라인에만 인가되어야만 한다. 도 8은 하나의 프레임에 관한 타이밍도이므로, 센싱 기간(특히, 전류 감지 기간)에 Sense 신호가 하나의 라인에 한번 인가된 것을 도시하고 있다.

- [0138] 한편, 디스플레이 패널(1000, 1000')은 하나의 영상 프레임을 디스플레이하기 위해서는 전체 픽셀 또는 전체 서 브 픽셀에 대해 진폭 설정 전압과 펄스 폭 설정 전압이 설정되어야 한다. 따라서, 디스플레이 패널(1000, 1000')은 하나의 영상 프레임에 대해 전체 가로 라인을 순차적으로 변경하면서 PWM 구동 회로(330) 및 PAM 구동 회로(310)에 펄스 폭 설정 전압 및 진폭 설정 전압이 각각 인가되어야 한다. 하나의 영상 프레임을 디스플레이

하기 위해 구동되는 신호들을 시간 순서에 따라 도시한 도 8에서, 제어 신호 SPWM  $1 \sim SPWM$  270 및 제어 신호 SPAM  $1 \sim SPWM$  270은 이와 같은 내용을 도시하고 있다.

- [0139] 한편, 본 개시의 실시 예들에 따르면, 제 2 구동 회로(300-2)는 디스플레이 패널(1000, 1000')에 포함된 발광 소자들(200)을 상술한 바와 같이 라인별로 제어하는 제어 신호를 생성하여 디스플레이 패널(1000, 1000')로 제공할 수 있다.

- [0140] 이하에서는, 도 10a 내지 도 11c를 참조하여 본 개시의 일 실시 예에 따른 제 2 구동 회로(300-2)의 구성 및 동작을 자세히 설명한다. 한편, 도 10a 내지 도 11c에 도시된 각종 전압이나 시간에 관한 수치는 하나의 실시 예에 불과하며, 해당 값에 한정되는 것은 아니다.

- [0141] 도 10a는 본 개시의 일 실시 예에 따른 제 1 구동부(370)를 구성하는 제 1 회로(210)의 회로도이다. 한편, 전술한 바와 같이, 디스플레이 패널(1000, 1000')은 영상 프레임마다 가로 라인을 순차적으로 변경하면서 제어 신호 (Sense)가 변경된 라인에 인가될 수 있다.

- [0142] 이를 위해, 각 라인마다 하나씩 구비된 제 1 회로(210-1 내지 210-270)는 도 10b와 같이 서로 연결될 수 있다. 도 10b를 보면, 하나의 라인에 대한 구동부 출력 신호(Sense)는, 상기 하나의 라인의 다음 라인에 대한 구동부의 스타트 신호(VST)로 입력되도록 상호 270개의 제 1 회로(210-1 내지 210-270)가 상호 연결되는 것을 볼 수있다. 도 10c를 보면 Sense 신호가 하나의 프레임당 한 번씩 라인을 변경하며 출력되는 것을 볼 수 있다.

- [0143] 한편, 도 10a 및 도 10c를 참조하여 하나의 Sense 제어 신호가 출력되는 과정을 살펴보면 다음과 같다. 먼저, Vst 신호가 입력되면, 트랜지스터(211)가 온되어 Q 단자 전압은 로우가 되고, 이에 따라 트랜지스터(214)가 온되어 QB 단자 전압은 하이(VDD)가 된다. 이때, 로우 전압은 캐피시터(213)에 충전된다. 이후, CLK 신호가 로우가 되면, Q 단자 전압은 부트 스트랩핑(Bootstrapping)되며, 이에 따라, 트랜지스터(216)가 완전히(fully) 턴은되어 Vout 즉, Sense #1 신호가 출력된다. 이후, Reset 신호가 로우로 인가되면, 트랜지스터(217)가 온되어 Q 단자 전압은 하이가 되고, 이에 따라, 트랜지스터(214)가 오프된다. 이때, CLK hold 신호가 로우로 인가되므로, QB 전압은 로우가 되어 커패시터(215)에 충전된 후 CLK hold 신호에 따라 로우가 유지된다. 이는 트랜지스터(214)가 오프되어 VDD와 연결이 끊어지기 때문이다. QB 단자 전압이 로우로 유지되는 시간은 리셋 신호가 인가된 후 다음 라인의 제 1 구동 회로(210-2)에 CLK 로우 신호가 인가될 때까지가 된다.

- [0144] 그 밖의 동작은 회로의 구성과 인가되는 신호와의 관계에서 당업자에게 자명하게 이해될 수 있으므로, 보다 자세한 설명은 생략한다.

- [0145] 이상과 같이, 제 1 회로(210-1 내지 210-270)를 연결하고, 신호를 제 1 회로(210-1 내지 210-270)에 인가함으로써, 제 1 구동부(370)는 하나의 프레임 당 한번씩 라인을 변경하며 출력되는 제어 신호 Sense를 생성할 수 있고, 생성된 제어 신호 Sense를 디스플레이 패널(1000, 1000')의 제 1 트랜지스터들(340)에 인가할 수 있다.

- [0146] 한편, 도 10a에서 CLK, CLKhold, VST, Reset과 같은 제 1 회로(210)로 인가되는 입력 신호들은 외부의 프로세서 또는 TCON(미도시)로부터 도 10c에 도시된 바와 같이 입력될 수 있다.

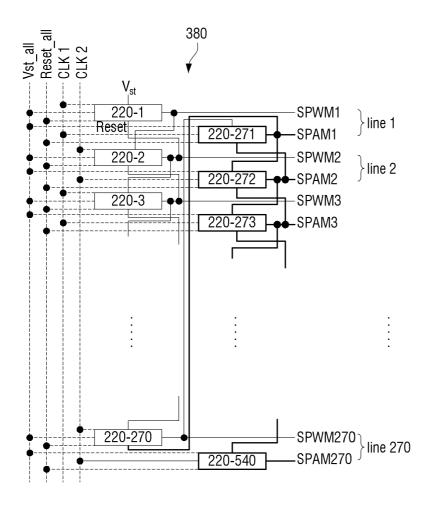

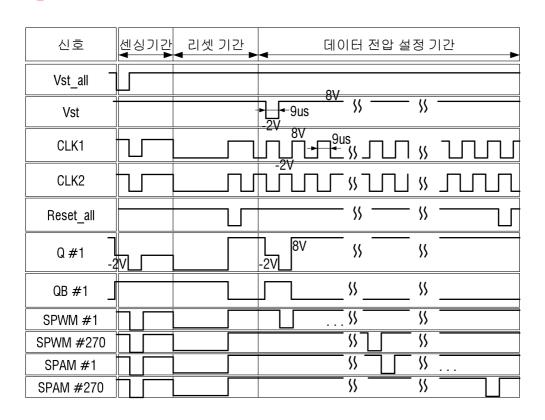

- [0147] 도 11a는 본 개시의 일 실시 예에 따른 제 2 구동부(380)를 구성하는 제 2 회로(220)의 회로도이다. 전술한 바와 같이, 디스플레이 패널(1000, 1000')은 하나의 영상 프레임에 대해 전체 가로 라인을 순차적으로 변경하면서 PWM 구동 회로 및 PAM 구동 회로에 펄스 폭 설정 전압 및 진폭 설정 전압이 각각 인가될 수 있다.

- [0148] 이를 위해, 제 2 구동부(380)를 구성하는 회로구성(220)은, 예를 들어, 220-1 및 220-271과 같이 각 라인마다 2 개씩 배치되며, 도 11b와 같이 서로 연결될 수 있다. 도 11b를 보면, 제 2 구동부(380)를 구성하는 하나의 제 2 회로(220-2)는, 이전 라인의 제 2 회로(220-1)의 출력 신호를 스타트 신호(Vst)로 입력받고, 제 2 회로(220-2)의 출력 신호가, 상기 이전 라인의 제 2 회로(220-1)의 리셋 신호(Reset)로 입력되도록 연결되는 것을 볼 수 있다.

- [0149] 한편, 제 2 회로(220)는, 도 10a의 제 1 회로(210) 회로와 비교할 때, 3개의 트랜지스터(T9, T10, T11)가 제어 신호 Vst\_all(전체 스타트) 및 Reset\_all(전체 리셋)과 관련하여 추가되었으며, 출력 신호 Vout이 SPWM 또는 SPAM 신호가 된다는 것을 제외하고 동일한 것을 볼 수 있다. 따라서, 당업자라면, 상술한 도 10a 및 도 10c에 관한 동작 설명, 도 11a의 회로 구성(220)의 구성 및 도 11c에 도시된 신호들의 타이밍도를 통해 제 2 회로 (220)의 동작을 자명하게 이해할 수 있을 것이다. 따라서, 보다 자세한 설명은 생략한다.

- [0150] 한편, 본 개시의 일 실시 예에 따르면, CLK 2 단자에 CLK 2 신호를 입력하는 대신 그라운드 전압(VSS)에 연결시 킬 수도 있다. 또한, 제 2 회로(220)로 인가되는 제어 신호 Vst\_all, Vst, CLK1, CLK2, Reset\_all 등은 외부의

프로세서 또는 TCON(미도시)로부터 도 11c에 도시된 바와 같이 입력될 수 있다.

- [0151] 한편, 예를 들어, 도 11c의 타이밍도는, 하나의 픽셀을 구성하는 서브 픽셀들(예를 들어, R, G, B 서브 픽셀)이 먹스(Multiplexer, MUX)를 통해 연결되지 않은 경우, 즉 먹스 미사용시 SPWM 및 SPAM 라인의 스캔 동작의 예를 도시한 것으로 볼 수 있다.

- [0152] 따라서, 먹스를 사용하는 경우, 즉, 먹스를 통해 R, G, B 서브 픽셀을 각각 구동하는 경우라면, 본 개시의 일실시 예에 따를 때, 도 11c의 SPWM 및 SPAM 라인의 스캔 동작은 서브 픽셀 별로 나누어 3번 반복 동작될 수 있을 것이다.

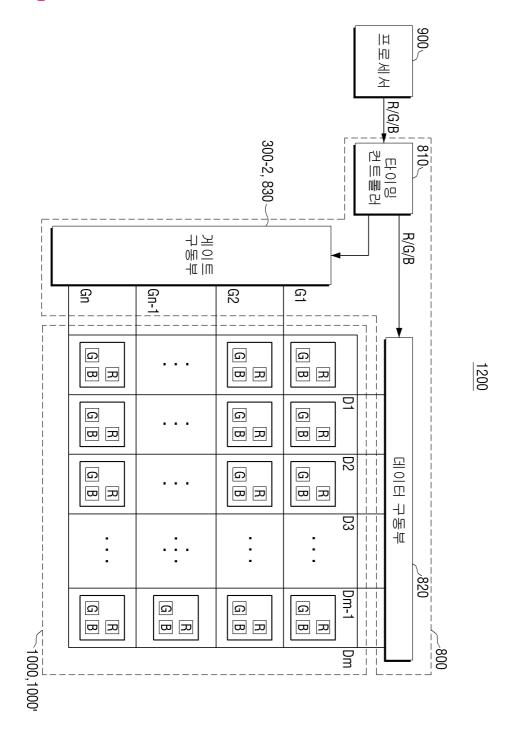

- [0153] 도 12는 본 개시의 일 실시 예에 따른 디스플레이 장치의 구성도이다. 도 12에 따르면, 디스플레이 장치(1200)는 디스플레이 패널(1000, 1000'), 패널 구동부(800) 및 프로세서(900)를 포함한다.

- [0154] 디스플레이 패널(1000, 1000')은 복수의 서브 픽셀을 구성하는 복수의 발광 소자(200) 및 각 발광 소자(200)들을 구동하기 위한 복수의 제 1 구동 회로(300-1)를 포함한다.

- [0155] 구체적으로, 디스플레이 패널(1000, 1000')은 게이트 라인들(G1 내지 Gn)과 데이터 라인들(D1 내지 Dm)이 상호 교차하도록 형성되고, 그 교차로 마련되는 영역에 제 1 구동 회로 구동 회로(300-1)가 형성될 수 있다. 예를 들어, 복수의 제 1 구동 회로(300-1) 각각은 인접한 R, G, B 서브 픽셀이 하나의 픽셀을 이루도록 구성될 수 있으나, 이에 한정되는 것은 아니다.

- [0156] 한편, 도 12에서는 도시의 편의를 위해, 게이트 구동부(830)(즉, 제 2 구동 회로(300-2), 이하에서는, 도 12에서는 게이트 구동부(830)로 통칭한다.)에서 디스플레이 패널(1000, 1000')에 포함된 각 제 1 구동 회로(300-1)에 제어 신호를 인가하기 위한 라인으로 하나의 게이트 신호 라인(G1 내지 Gn)을 도시하였지만, 각 게이트 신호 라인은 Sense 라인(Sense 1 내지 Sense n), SPWM 라인(SPWM 1 내지 SPWM n) 및 SPAM 라인(SPAM 1 내지 SPAM n)을 포함할 수 있다.

- [0157] 패널 구동부(800)는 프로세서(900)의 제어에 따라 디스플레이 패널(1000, 1000')(보다 구체적으로는, 복수의 제 1 구동 회로(300-1) 각각)을 구동하며, 타이밍 컨트롤러(810), 데이터 구동부(820) 및 게이트 구동부(830)를 포함할 수 있다.

- [0158] 타이밍 컨트롤러(810)는 외부로부터 입력 신호(IS), 수평 동기 신호(Hsync), 수직 동기 신호(Vsync) 및 메인 클 럭 신호(MCLK) 등을 입력받아 영상 데이터 신호, 주사 제어 신호, 데이터 제어 신호, 발광 제어 신호 등을 생성하여 디스플레이 패널(1000, 1000'), 데이터 구동부(820), 게이트 구동부(830) 등에 제공할 수 있다.

- [0159] 특히, 타이밍 컨트롤러(810)는, 본 개시의 다양한 실시 예들에 따라, 제어 신호(Ref), 제어 신호(Sweep), 제어 신호(RES), 제어 신호(Control), 제어 신호(MUX Sel R, G, B)를 제 1 구동 회로(300-1)에 인가할 수 있다.

- [0160] 데이터 구동부(820)(또는 소스 드라이버, 데이터 드라이버)는, 데이터 신호를 생성하는 수단으로, 프로세서 (900)로부터 R/G/B 성분의 영상 데이터 등 전달받아 데이터 신호(예를 들어, 특정 전압, 진폭 설정 전압 및 펄스 폭 설정 전압)를 생성한다. 또한, 데이터 구동부(820)는 생성된 데이터 신호를 디스플레이 패널(1000, 1000')에 인가할 수 있다.

- [0161] 게이트 구동부(830)(또는, 게이트 드라이버)는 제어 신호(Sense), 제어 신호(SPWM), 제어 신호(SPAM) 등 각종 제어 신호를 생성하는 수단으로, 생성된 각종 제어 신호를 디스플레이 패널(100)의 특정한 행(또는, 특정한 가로 라인)에 전달한다.

- [0162] 특히, 제어 신호(Sense)가 전달된 제 1 구동 회로(300-1)는 제 1 트랜지스터(340)가 온되어 구동 트랜지스터 (325)를 흐르는 전류가 데이터 라인(5)을 통해 감지될 수 있다. 또한, 제어 신호(SPAM)가 전달된 제 1 구동 회로(300-1)는 제 2 트랜지스터(311)가 온되어 데이터 구동부(820)에서 출력된 진폭 설정 전압이 데이터 라인(5)을 통해 전달될 수 있다. 또한, 제어 신호(SPWM)가 전달된 제 1 구동 회로(300-1)는 제 3 트랜지스터(336)가 온되어 데이터 구동부(820)에서 출력된 필스 폭 설정 전압이 데이터 라인(5)을 통해 전달될 수 있다.

- [0163] 이를 위해, 게이트 구동부(830)는 도 10a 내지 도 11c를 통해 전술한 바와 같이, 구성 및 동작될 수 있다.

- [0164] 또한, 게이트 구동부(830)는, 실시 예에 따라 제 1 구동 회로(300-1)의 구동 전압 단자(321)에 구동 전압(VDD)을 인가할 수 있다.

- [0165] 한편, 데이터 구동부(820) 및 게이트 구동부(830)는, 전술한 바와 같이, 그 전/일부가 디스플레이 패널(1000,

1000')의 글래스(100) 일면에 형성된 구동 회로 층(300, 300')에 포함되도록 구현되거나 별도의 반도체 IC로 구현되어 글래스(100)의 타 면에 배치될 수 있다.

- [0166] 프로세서(900)는 디스플레이 장치(1200)의 전반적인 동작을 제어한다. 특히, 프로세서(900)는 패널 구동부(80 0)를 제어하여 디스플레이 패널(1000, 1000')을 구동함으로써, 제 1 및 제 2 구동 회로(300-1, 300-2)가 상술한 동작들을 수행하도록 할 수 있다.

- [0167] 이를 위해, 프로세서(900)는 중앙처리장치(central processing unit(CPU)), micro-controller, 어플리케이션 프로세서(application processor(AP)), 또는 커뮤니케이션 프로세서(communication processor(CP)), ARM 프로 세서 중 하나 이상으로 구현될 수 있다.

- [0168] 구체적으로, 본 개시의 일 실시 예에 따르면, 프로세서(900)는, 펄스 폭 설정 전압에 따라 구동 전류의 펄스 폭을 설정하고, 진폭 설정 전압에 따라 구동 전류의 진폭을 설정하도록 패널 구동부(800)를 제어할 수 있다. 이때, 프로세서(900)는 디스플레이 패널(1000, 1000')이 n 개의 행과 m 개의 열로 구성된 경우, 행 단위(가로라인 단위)로 구동 전류의 진폭이나 펄스 폭이 설정되도록 패널 구동부(800)를 제어할 수 있다.

- [0169] 이후, 프로세서(900)는 디스플레이 패널(1000, 1000')에 포함된 복수의 제 1 구동 회로(300-1)의 전류원(320)을 통해 발광 소자(200)에 일제히 구동 전압(VDD)을 인가하고, 복수의 제 1 구동 회로(300-1) 각각의 PWM 구동 회로(330)에 선형 변화 전압(스위프 전압)이 인가되도록 패널 구동부(800)를 제어함으로써, 영상을 디스플레이할 수 있다.

- [0170] 이때, 프로세서(900)가 패널 구동부(800)를 제어하여 디스플레이 패널(1000, 1000')에 포함된 제 1 및 제 2 구동 회로(300-1, 300-2)의 동작을 제어하는 구체적인 내용은 전술한 바와 같으므로, 중복 설명은 생략하기로 한다.

- [0171] 한편, 전술한 예에서는 프로세서(900)와 타이밍 컨트롤러(810)를 별도의 구성요소로 설명하였으나, 프로세서 (900) 없이, 타이밍 컨트롤러(810)가 프로세서(900)의 기능을 수행할 수도 있다.

- [0172] 이상에서는, 발광 소자(200)가 마이크로 LED인 것을 예로 들어 설명하였으나, 이에 한정되는 것은 아니다. 즉, 실시 예에 따라 발광 소자(200)가 100 마이크로미터이상의 크기를 갖는 LED인 경우에도 상술한 본 개시의 다양한 실시 예들에 따른 제 1 및 제 2 구동 회로(300-1, 300-2)가 적용될 수 있음은 물론이다.

- [0173] 또한, 이상에서는, 디스플레이 패널(1000, 1000')이 COG 타입인 것을 예로 들어 설명하였으나, 실시 예에 따라 COB 타입의 디스플레이 패널에도 상술한 본 개시의 다양한 실시 예들에 따른 제 1 및 제 2 구동 회로(300-1, 300-2)가 적용될 수 있을 것이다. COB 타입의 디스플레이 패널의 경우, COG 방식과는 달리 글래스(100) 대신 기판이 이용되는 데, 이 경우 기판을 관통하는 홀을 형성하고, 홀을 통해 기판의 일면과 타면을 전기적으로 연결 함으로써, 기판의 일 면에 마련된 구동 회로층(300)과 기판의 타 면에 마련된 각종 회로들이 전기적으로 연결될 수 있을 것이다.

- [0174] 한편, 본 개시의 일 실시 예에 따르면, 디스플레이 패널(1000, 1000')은 확장성 없는 독립적인 디스플레이 패널 로 구현될 수 있다. 그러나, 이에 한정되는 것은 아니며, 대면적의 타일드 디스플레이의 일부를 구성하는 확장 가능한 디스플레이 모듈로 구현될 수도 있다.

- [0175] 이상 설명한 바와 같이 본 개시의 다양한 실시 예에 따르면, 디스플레이 패널에 포함된 발광 소자의 계조에 따른 파장 변화를 방지할 수 있다. 또한, 디스플레이 패널을 구성하는 발광 소자의 얼룩이나 색상을 보정할 수 있다. 또한, 복수의 모듈라(modular) 디스플레이 패널을 조합하여 대면적의 타일드(tiled) 디스플레이 패널을 구성할 경우에도 각 모듈라 디스플레이 패널 간의 휘도나 색상 차이를 보정할 수 있다.

- [0176] 한편, 본 개시의 다양한 실시 예들은 기기(machine)(예: 컴퓨터)로 읽을 수 있는 저장 매체(machine-readable storage media)에 저장된 명령어를 포함하는 소프트웨어로 구현될 수 있다. 여기서, 기기는, 저장 매체로부터 저장된 명령어를 호출하고, 호출된 명령어에 따라 동작이 가능한 장치로서, 개시된 실시 예들에 따른 디스플레이 장치(1200)를 포함할 수 있다.

- [0177] 상기 명령이 프로세서에 의해 실행될 경우, 프로세서가 직접, 또는 상기 프로세서의 제어하에 다른 구성요소들을 이용하여 상기 명령에 해당하는 기능을 수행할 수 있다. 명령은 컴파일러 또는 인터프리터에 의해 생성 또는 실행되는 코드를 포함할 수 있다. 기기로 읽을 수 있는 저장매체는, 비일시적(non-transitory) 저장매체의 형태로 제공될 수 있다. 여기서, '비일시적'은 저장매체가 신호(signal)를 포함하지 않으며 실재(tangible)한다는

것을 의미할 뿐 데이터가 저장매체에 반영구적 또는 임시적으로 저장됨을 구분하지 않는다.

- [0178] 일 실시 예에 따르면, 본 개시에 개시된 다양한 실시 예들에 따른 방법은 컴퓨터 프로그램 제품(computer program product)에 포함되어 제공될 수 있다. 컴퓨터 프로그램 제품은 상품으로서 판매자 및 구매자 간에 거래될 수 있다. 컴퓨터 프로그램 제품은 기기로 읽을 수 있는 저장 매체(예: compact disc read only memory (CD-ROM))의 형태로, 또는 어플리케이션 스토어(예: 플레이 스토어TM)를 통해 온라인으로 배포될 수 있다. 온라인 배포의 경우에, 컴퓨터 프로그램 제품의 적어도 일부는 제조사의 서버, 어플리케이션 스토어의 서버, 또는 중계서버의 메모리와 같은 저장 매체에 적어도 일시 저장되거나, 임시적으로 생성될 수 있다.

- [0179] 다양한 실시 예들에 따른 구성 요소(예: 모듈 또는 프로그램) 각각은 단수 또는 복수의 개체로 구성될 수 있으며, 전술한 해당 서브 구성 요소들 중 일부 서브 구성 요소가 생략되거나, 또는 다른 서브 구성 요소가 다양한 실시 예에 더 포함될 수 있다. 대체적으로 또는 추가적으로, 일부 구성 요소들(예: 모듈 또는 프로그램)은 하나의 개체로 통합되어, 통합되기 이전의 각각의 해당 구성 요소에 의해 수행되는 기능을 동일 또는 유사하게 수행할 수 있다. 다양한 실시 예들에 따른, 모듈, 프로그램 또는 다른 구성 요소에 의해 수행되는 동작들은 순차적, 병렬적, 반복적 또는 휴리스틱하게 실행되거나, 적어도 일부 동작이 다른 순서로 실행되거나, 생략되거나, 또는 다른 동작이 추가될 수 있다.

- [0180] 이상의 설명은 본 개시의 기술 사상을 예시적으로 설명한 것에 불과한 것으로서, 본 개시가 속하는 기술 분야에서 통상의 지식을 가진 자라면 본 개시의 본질적인 특성에서 벗어나지 않는 범위에서 다양한 수정 및 변형이 가능할 것이다. 또한, 본 개시에 따른 실시 예들은 본 개시의 기술 사상을 한정하기 위한 것이 아니라 설명하기한 것이고, 이러한 실시 예에 의하여 본 개시의 기술 사상의 범위가 한정되는 것은 아니다. 따라서, 본 개시의 보호 범위는 아래의 청구범위에 의하여 해석되어야 하며, 그와 동등한 범위 내에 있는 모든 기술 사상은 본 개시의 권리범위에 포함되는 것으로 해석되어야 할 것이다.

#### 부호의 설명

[0181] 200 : 발광 소자 300 : 구동 회로층

300-1 : 제 1 구동 회로 300-2 : 제 2 구동 회로

도면

# 도면2a

1000

# 도면2b

# 도면3

도면4a

# 도면4b

# 도면5a

# *도면5b*

도면6

# 도면10a

# 도면10b

# 도면10c

# 도면11a

# 도면11b

# 도면11c

도면12

| 专利名称(译)        | 显示屏                                                               |         |            |  |

|----------------|-------------------------------------------------------------------|---------|------------|--|

| 公开(公告)号        | KR1020190137658A                                                  | 公开(公告)日 | 2019-12-11 |  |

| 申请号            | KR1020180097404                                                   | 申请日     | 2018-08-21 |  |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                          |         |            |  |

| 申请(专利权)人(译)    | 三星电子有限公司                                                          |         |            |  |

| [标]发明人         | 김진호<br>강기선<br>신상민<br>이호섭<br>정영기                                   |         |            |  |

| 发明人            | 김진호<br>강기선<br>신상민<br>이호섭<br>정영기                                   |         |            |  |

| IPC分类号         | G09G3/3233                                                        |         |            |  |

| CPC分类号         | G09G3/3233 G09G2300/0452 G09G2320/0233 G09G2320/0242 G09G2330/028 |         |            |  |

| 代理人(译)         | 정홍식<br>Gimtaeheon                                                 |         |            |  |

| 优先权            | 1020180063604 2018-06-01 KF                                       | ₹       |            |  |

| 外部链接           | Espacenet                                                         |         |            |  |

|                |                                                                   |         |            |  |

# 摘要(译)

公开了一种能够校正每个显示面板模块之间的亮度或色差的显示面板。本发明的显示面板包括:驱动电路层,其形成在玻璃上并包括第一和第二驱动电路;以及 发光元件安装在驱动电路层上并与第一驱动电路电连接并构成显示面板的子像素。 第一驱动电路包括:PAM驱动电路,用于控制提供给无机发光元件的驱动电流的幅度;以及PWM驱动电路,用于控制无机发光元件的发光时间。 第二驱动电路被布置在除了在驱动电路层中布置第一驱动电路的区域之外的区域中,并且第二驱动电路生成用于将第一驱动电路驱动到第一驱动电路的控制信号。